SY100S350

SY100S350 is Hex D-latch manufactured by Micrel Semiconductor.

Micrel, Inc.

HEX D-LATCH

Features

DESCRIPTION s Max. transparent propagation delay of 900ps s Min. Master Reset and Enable pulse widths of 100ps s IEE min. of

- 98m A s Industry standard 100K ECL levels s Extended supply voltage option:

VEE =

- 4.2V to

- 5.5V s Voltage and temperature pensation for improved noise immunity s Internal 75kΩ input pull-down resistors s More than 40% faster than Fairchild s Approximately 30% lower power than Fairchild s Function and pinout patible with Fairchild F100K s Available in 28-pin PLCC package

The SY100S350 offers six high-speed D-Latches with both true and plement outputs, and is performance patible for use with high-performance ECL systems. When both enable signals (Ea and Eb) are at a logic LOW, the latches are transparent and the input signals( D0- D5) appear at the outputs (Q0- Q5) after a propagation delay. If either or both of the enable signals are at a logic HIGH, then the latches store the last valid data present on its inputs before Ea or Eb went to a logic HIGH. The Master Reset (MR) overrides all other input signals and takes the outputs to a logic LOW state. All inputs have 75kΩ pull-down resistors.

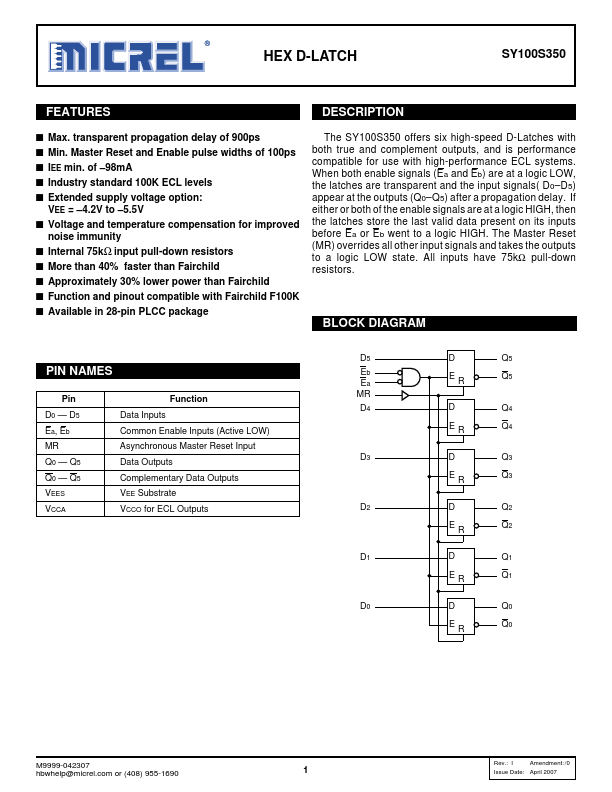

BLOCK DIAGRAM

PIN NAMES

Pin D0

- D5 Ea, Eb MR Q0

- Q5 Q0

- Q5 VEES VCCA

Function Data Inputs mon Enable Inputs (Active LOW) Asynchronous Master Reset Input Data Outputs plementary Data Outputs VEE Substrate VCCO for ECL Outputs

D5 D Q5

Eb Ea

E R Q5

D4 D Q4

E R Q4

D3 D Q3 E R Q3

D2 D Q2 E R Q2

D1 D Q1 E R Q1

D0 D Q0 E R Q0

M9999-042307 hbwhelp@micrel. or (408) 955-1690

Rev.: I

Amendment: /0

Issue Date: April 2007

Micrel,...