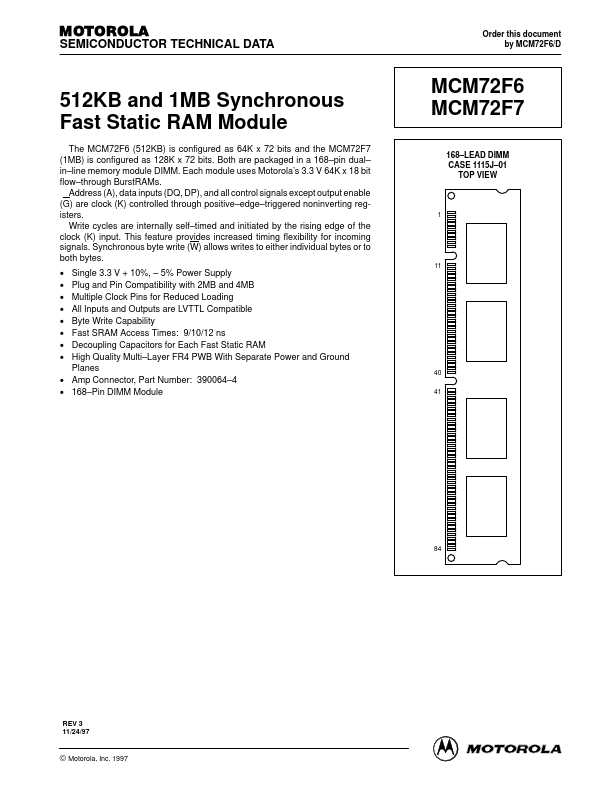

| Part | MCM72F6 |

|---|---|

| Description | 512KB and 1MB Synchronous Fast Static RAM Module |

| Manufacturer | Motorola Semiconductor |

| Size | 160.33 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| HFDOM40B-xxxSx | Hanbit Electronics | 40Pin Flash Disk Module |

| HFDOM44P-xxxSx | Hanbit Electronics | 44Pin Flash Disk Module |

| HFDOM40P-xxxSx | Hanbit Electronics | 40Pin Flash Disk Module |