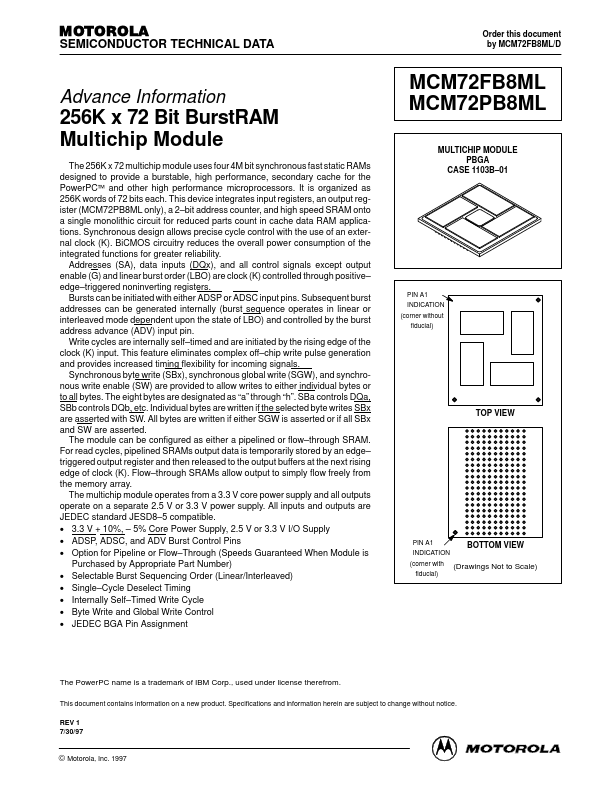

MCM72FB8ML Overview

Key Features

- eliminates complex off–chip write pulse generation and provides increased timing flexibility for incoming signals

- The eight bytes are designated as “a” through “h”

- SBa controls DQa, SBb controls DQb, etc

- Individual bytes are written if the selected byte writes SBx are asserted with SW

- All bytes are written if either SGW is asserted or if all SBx and SW are asserted

- The module can be configured as either a pipelined or flow–through