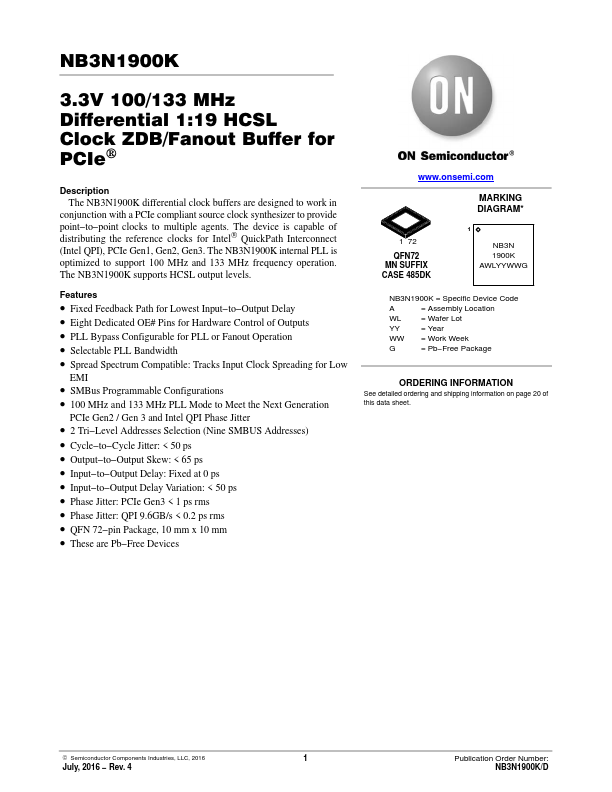

NB3N1900K

NB3N1900K is 3.3V 100/133MHz Differential 1:19 HCSL Clock ZDB/Fanout Buffer manufactured by onsemi.

3.3V 100/133 MHz Differential 1:19 HCSL Clock ZDB/Fanout Buffer for PCIe[

Description The NB3N1900K differential clock buffers are designed to work in conjunction with a PCIe pliant source clock synthesizer to provide point- to- point clocks to multiple agents. The device is capable of distributing the reference clocks for Intel® Quick Path Interconnect (Intel QPI), PCIe Gen1, Gen2, Gen3. The NB3N1900K internal PLL is optimized to support 100 MHz and 133 MHz frequency operation. The NB3N1900K supports HCSL output levels.

Features

- Fixed Feedback Path for Lowest Input- to- Output Delay

- Eight Dedicated OE# Pins for Hardware Control of Outputs

- PLL Bypass Configurable for PLL or Fanout Operation

- Selectable PLL Bandwidth

- Spread Spectrum patible: Tracks Input Clock Spreading for Low

- SMBus Programmable Configurations

- 100 MHz and 133 MHz PLL Mode to Meet the Next Generation

PCIe Gen2 / Gen 3 and Intel QPI Phase Jitter

- 2 Tri- Level...