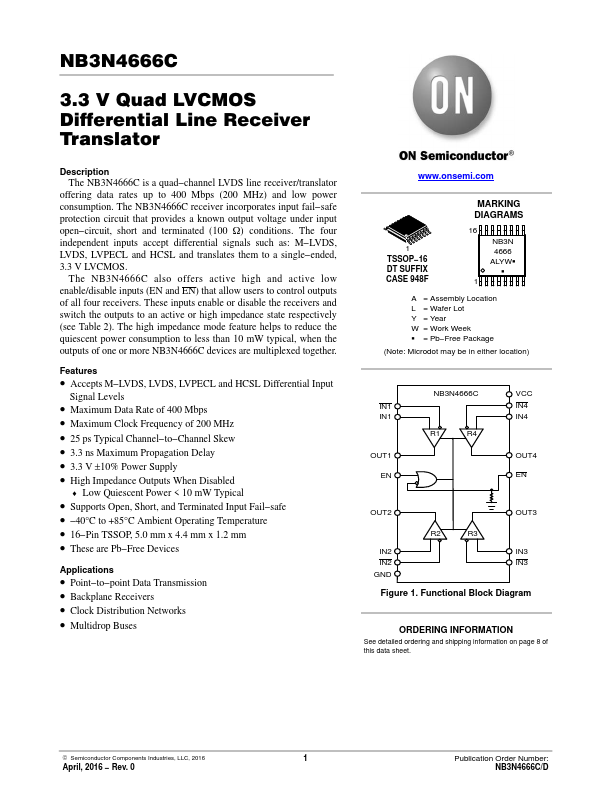

NB3N4666C Key Features

- Accepts M-LVDS, LVDS, LVPECL and HCSL Differential Input

- Maximum Data Rate of 400 Mbps

- Maximum Clock Frequency of 200 MHz

- 25 ps Typical Channel-to-Channel Skew

- 3.3 ns Maximum Propagation Delay

- 3.3 V ±10% Power Supply

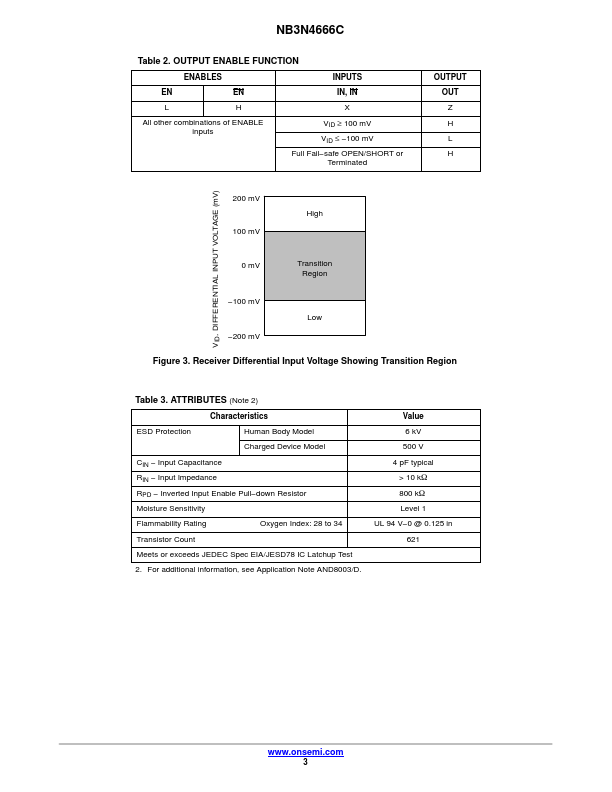

- High Impedance Outputs When Disabled

- Low Quiescent Power < 10 mW Typical

- Supports Open, Short, and Terminated Input Fail-safe

- 40°C to +85°C Ambient Operating Temperature