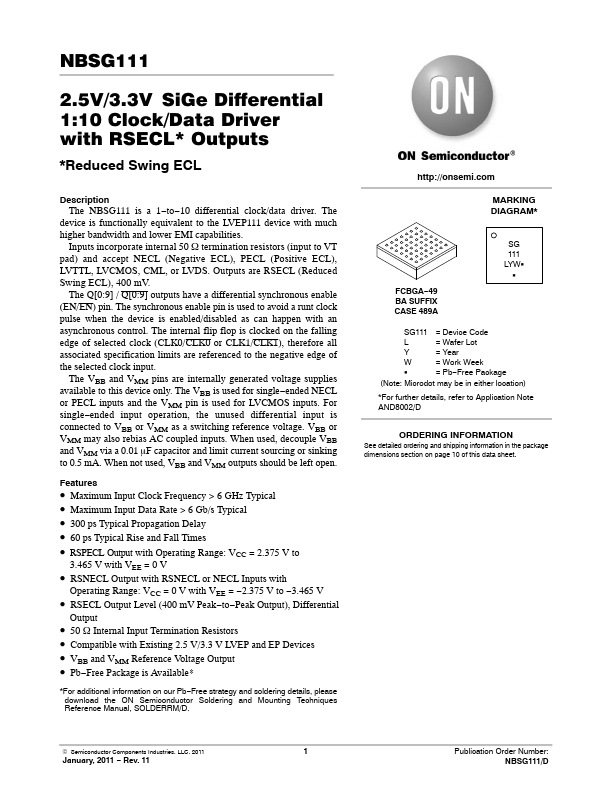

NBSG111

NBSG111 is 2.5V/3.3V SiGe Differential 1:10 Clock/Data Driver manufactured by onsemi.

Description

The NBSG111 is a 1- to- 10 differential clock/data driver. The device is functionally equivalent to the LVEP111 device with much higher bandwidth and lower EMI capabilities.

Inputs incorporate internal 50 W termination resistors (input to VT pad) and accept NECL (Negative ECL), PECL (Positive ECL), LVTTL, LVCMOS, CML, or LVDS. Outputs are RSECL (Reduced Swing ECL), 400 m V.

The Q[0:9] / Q[0:9] outputs have a differential synchronous enable (EN/EN) pin. The synchronous enable pin is used to avoid a runt clock pulse when the device is enabled/disabled as can happen with an asynchronous control. The internal flip flop is clocked on the falling edge of selected clock (CLK0/CLK0 or CLK1/CLK1), therefore all associated specification limits are referenced to the negative edge of the selected clock input.

The VBB and VMM pins are internally generated voltage supplies available to this device only. The VBB is used for single- ended NECL or PECL inputs and the VMM pin is used for LVCMOS inputs. For single- ended input operation, the unused differential input is connected to VBB or VMM as a switching reference voltage. VBB or VMM may also rebias AC coupled inputs. When used, decouple VBB and VMM via a 0.01 m F capacitor and limit current sourcing or sinking to 0.5 m A. When not used, VBB and VMM outputs should be left open.

Features

- Maximum Input Clock Frequency > 6 GHz Typical

- Maximum Input Data Rate > 6 Gb/s Typical

- 300 ps Typical Propagation Delay

- 60 ps Typical Rise and Fall Times

- RSPECL Output with Operating Range: VCC = 2.375 V to

3.465 V with VEE = 0 V

- RSNECL Output with RSNECL or NECL Inputs with

Operating Range: VCC = 0 V with VEE =

- 2.375 V to

- 3.465 V

- RSECL Output Level (400 m V Peak- to- Peak Output), Differential

Output

- 50 W Internal Input Termination Resistors

- patible with Existing 2.5 V/3.3 V LVEP and EP Devices

- VBB and VMM Reference Voltage Output

- Pb- Free Package is Available-

- For additional information on our Pb- Free strategy and...