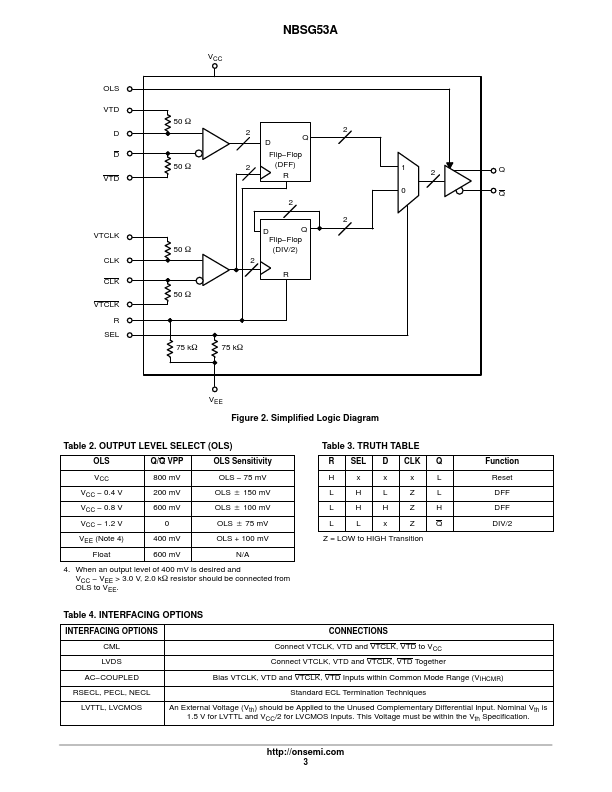

NBSG53A Description

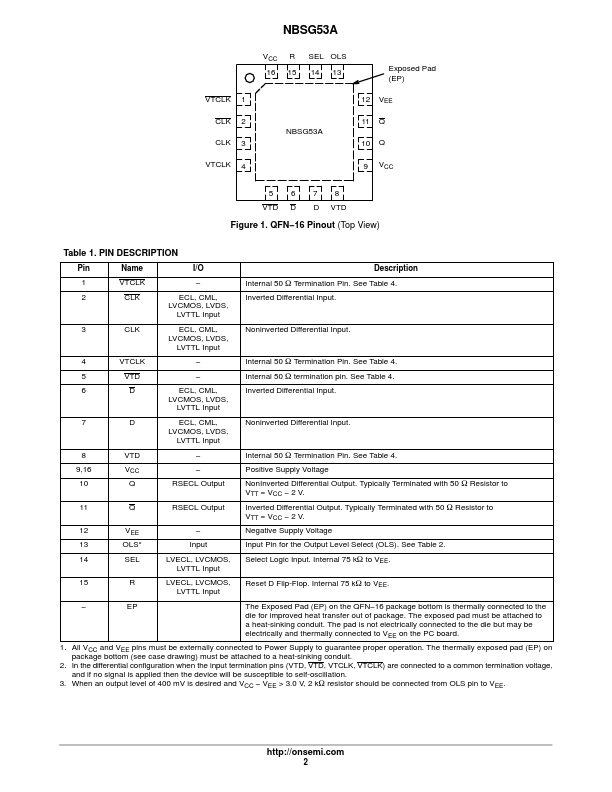

Pin Name I/O Description 1 VTCLK − Internal 50 W Termination Pin. 2 CLK ECL, CML, Inverted Differential Input. LVCMOS, LVDS, LVTTL Input 3 CLK ECL, CML, Noninverted Differential Input.

NBSG53A Key Features

- Maximum Input Clock Frequency (DFF) > 8 GHz Typical

- Maximum Input Clock Frequency (DIV/2) > 10 GHz Typical

- 210 ps Typical Propagation Delay (OLS = FLOAT)

- 45 ps Typical Rise and Fall Times (OLS = FLOAT)

- DIV/2 Mode (Active with Select Low)

- DFF Mode (Active with Select High)

- Selectable Swing PECL Output with Operating Range: VCC = 2.375 V

- Selectable Output Level (0 V, 200 mV, 400 mV, 600 mV, or 800 mV

- 50 W Internal Input Termination Resistors on all Differential Inputs

- These are Pb-Free Devices