RC31012A

RC31012A is VersaClock 7 Programmable Jitter Attenuator manufactured by Renesas.

- Part of the RC31008A comparator family.

- Part of the RC31008A comparator family.

Features

- 169fs RMS typical phase jitter

- PCIe® Gen6 mon Clock (CC) 27fs RMS

- pliant with ITU-T G.8262 and G.8262.1 for synchronous Ethernet Equipment Clock (EEC/e EEC)

- Jitter attenuation with programmable loop bandwidth from 0.1Hz to 12k Hz

- 1k Hz to 650MHz LVDS/LP-HCSL outputs

- 1k Hz to 200MHz LVCMOS outputs

- Simple AC-coupling to LVPECL and CML

- Integrated 100 and 85 LP-HCSL terminations

- JESD204B/C support on differential or singleended outputs with DC-coupling or AC-coupling

- Up to four single-ended or two differential clock inputs; one crystal/TCXO/OCXO input

- Programmable General Purpose Inputs (GPI × 4) and General Purpose Input/Outputs (GPIO × 5)

- 1MHz I2C, 400k Hz SMBus, or 20MHz SPI support Configuration via internal One-Time Programmable (OTP) memory (up to 27 different configurations), serial interface, or external I2C EEPROM.

- Factory programmable internal OTP

- 1.8V, 2.5V, 3.3V, -40° to +85°C operation

- RC31012A

- 12 differential/24 single-ended outputs

- 6 × 6 × 0.9 mm 48-QFN package

- RC31008A

- 8 differential/16 single-ended outputs

- 5 × 5 × 0.9 mm 40-QFN package with optional integrated crystal

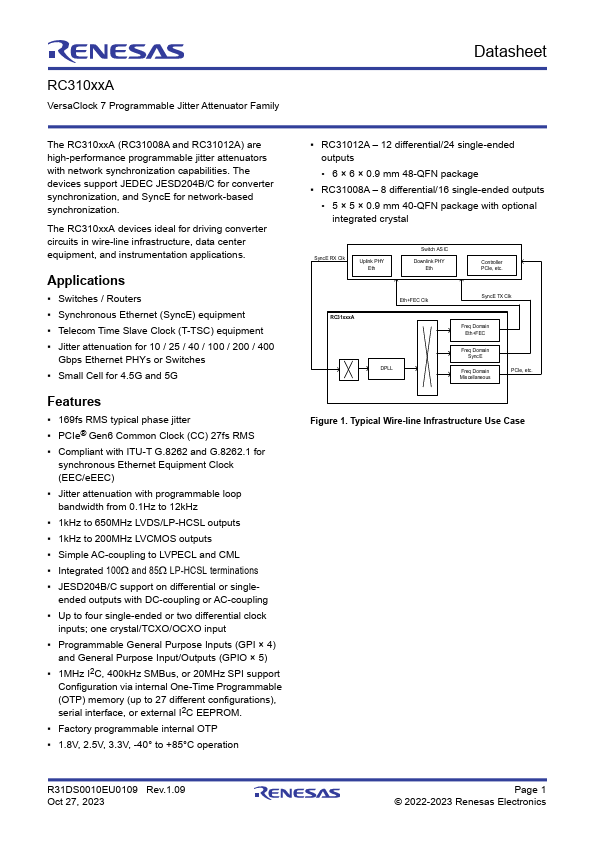

Sync E RX Clk

Uplink PHY Eth

Switch ASIC

Downlink PHY Eth

Controller PCIe, etc.

RC31xxx A

Eth+FEC Clk

DPLL

Sync E TX Clk

Freq Domain Eth+FEC

Freq Domain Sync E

Freq Domain Miscellaneous

PCIe, etc.

Figure 1. Typical Wire-line Infrastructure Use Case

R31DS0010EU0109 Rev.1.09 Oct 27, 2023

Page 1 © 2022-2023 Renesas Electronics

RC310xx A Datasheet

RC310xx A Block Diagram

XIN_REFIN...