STP5950 Key Features

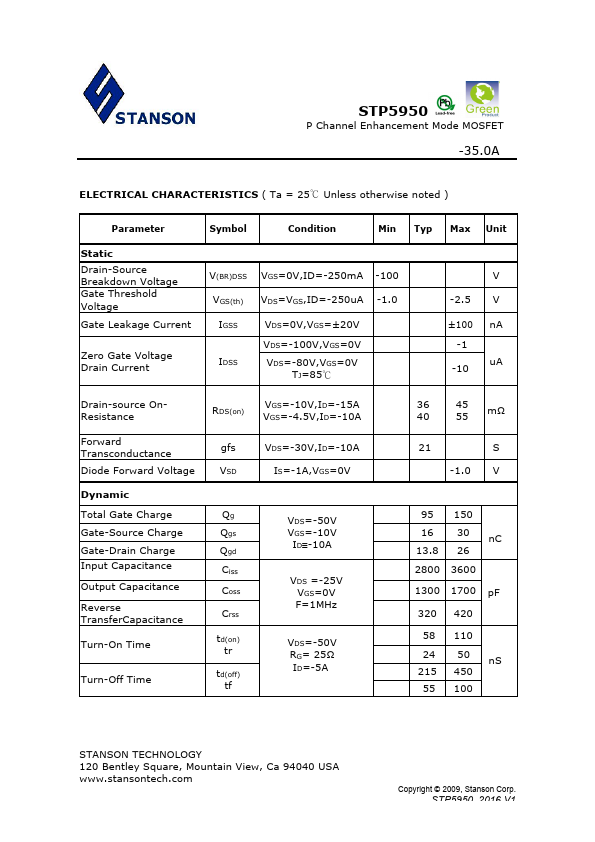

- 100V/-15A, RDS(ON) = 36mΩ (Typ.) @VGS = -10V

- 100V/-10A, RDS(ON) = 40mΩ @VGS = -4.5V

- Super high density cell design for extremely low RDS(ON)

- Exceptional on-resistance and maximum DC current capability

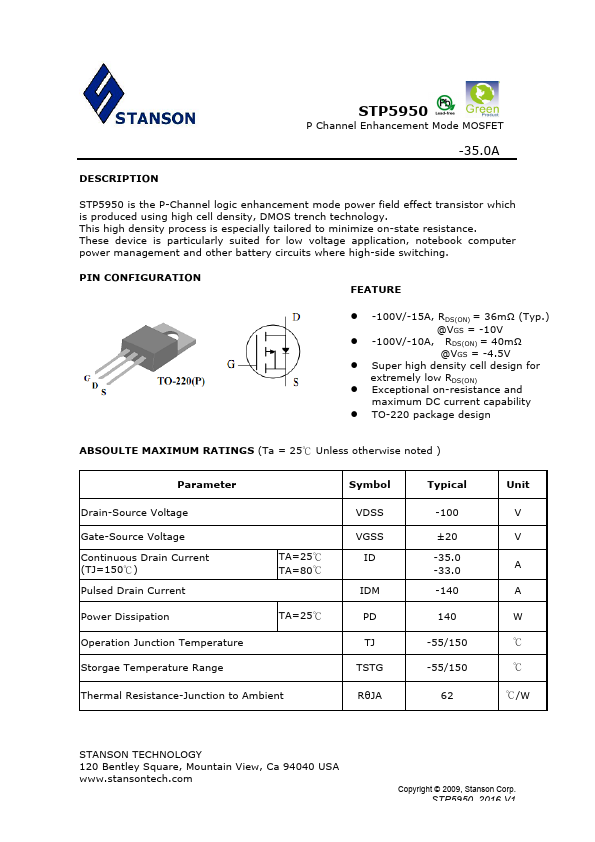

- TO-220 package design ABSOULTE MAXIMUM RATINGS (Ta = 25℃ Unless otherwise noted ) Parameter Drain-Source Vo