Datasheet Summary

CMOS SDRAM

2Mx8 SDRAM

1M x 8bit x 2 Banks Synchronous DRAM LVTTL

Revision 1.0 October 1999

Samsung Electronics reserves the right to change products or specification without notice.

-1-

Rev. 1.0 (Oct. 1999)

Revision History

Revision 1.0 (October 1999)

CMOS SDRAM

-2-

Rev. 1.0 (Oct. 1999)

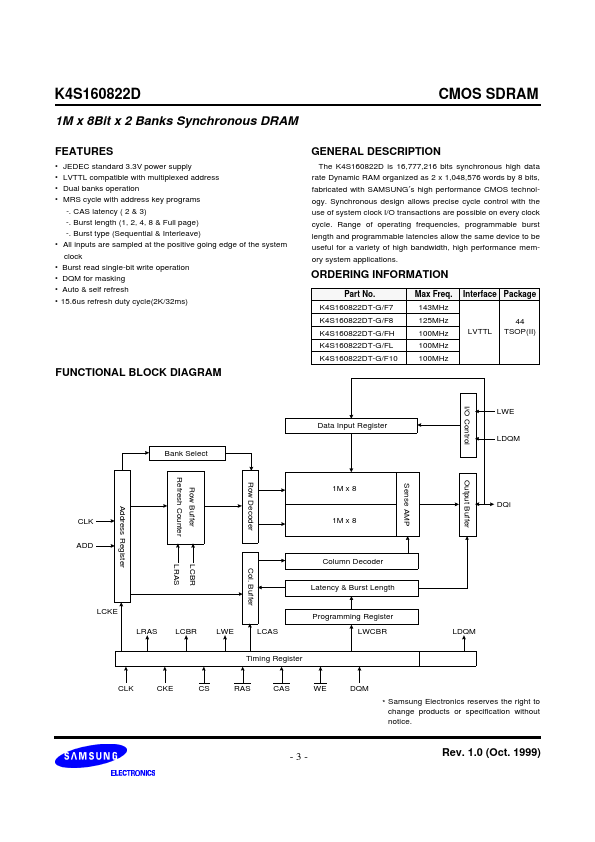

1M x 8Bit x 2 Banks Synchronous DRAM

Features

- -

- - JEDEC standard 3.3V power supply LVTTL patible with multiplexed address Dual banks operation MRS cycle with address key programs -. CAS latency ( 2 & 3) -. Burst length (1, 2, 4, 8 & Full page) -. Burst type (Sequential & Interleave) All inputs are sampled at the positive going edge of the system clock Burst...