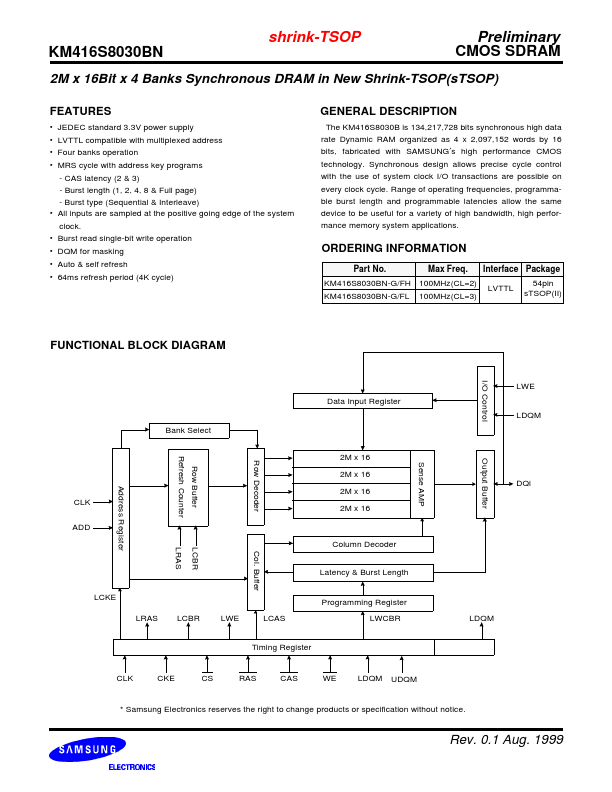

KM416S8030BN Key Features

- JEDEC standard 3.3V power supply

- LVTTL patible with multiplexed address

- Four banks operation

- MRS cycle with address key programs

- CAS latency (2 & 3)

- Burst length (1, 2, 4, 8 & Full page)

- Burst type (Sequential & Interleave)

- All inputs are sampled at the positive going edge of the system clock

- Burst read single-bit write operation

- DQM for masking