Datasheet Summary

White Electronic Designs

4Mx72 Synchronous DRAM-

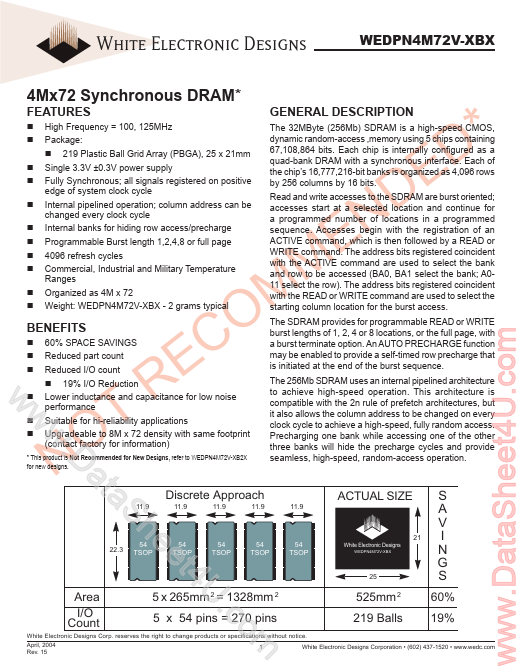

Features

- -

- -

- -

- -

- -

- Package:

- 219 Plastic Ball Grid Array (PBGA), 25 x 21mm Single 3.3V ±0.3V power supply Fully Synchronous; all signals registered on positive edge of system clock cycle Internal pipelined operation; column address can be changed every clock cycle Internal banks for hiding row access/precharge Programmable Burst length 1,2,4,8 or full page 4096 refresh cycles mercial, Industrial and Military Temperature Ranges Organized as 4M x 72 Weight: WEDPN4M72V-XBX

- 2 grams typical High Frequency = 100, 125MHz

WEDPN4M72V-XBX

GENERAL DESCRIPTION

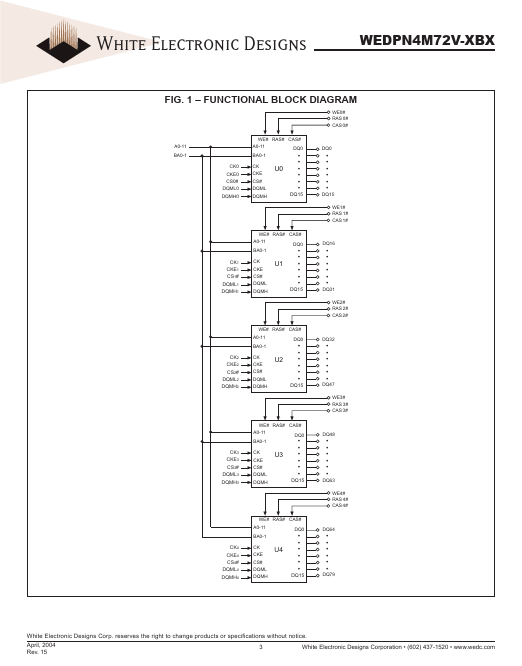

The 32MByte (256Mb) SDRAM is a high-speed CMOS, dynamic random-access...