ZL30112

ZL30112 is SLIC/CODEC DPLL manufactured by Zarlink Semiconductor.

ZL30112 SLIC/CODEC DPLL

Data Sheet

Features

November 2009

- Synchronizes to 8 kHz, 2.048 MHz, 8.192 MHz or 19.44 MHz input

- Provides 2.048 MHz and 8.192 MHz output clocks and an 8 kHz framing pulse

- Automatic entry and exit from freerun mode on reference fail

Ordering Information

ZL30112LDG1

32 Pin QFN- Trays, Bake & Drypack

- Pb Free Matte Tin -40°C to +85°C

- Provides DPLL lock and reference fail indication

- DPLL bandwidth of 29 Hz for all rates of input references

- Less than 0.6 nsecpp intrinsic jitter on all output clocks

- 20 MHz external master clock source: clock oscillator or crystal

- Simple hardware control interface

Applications

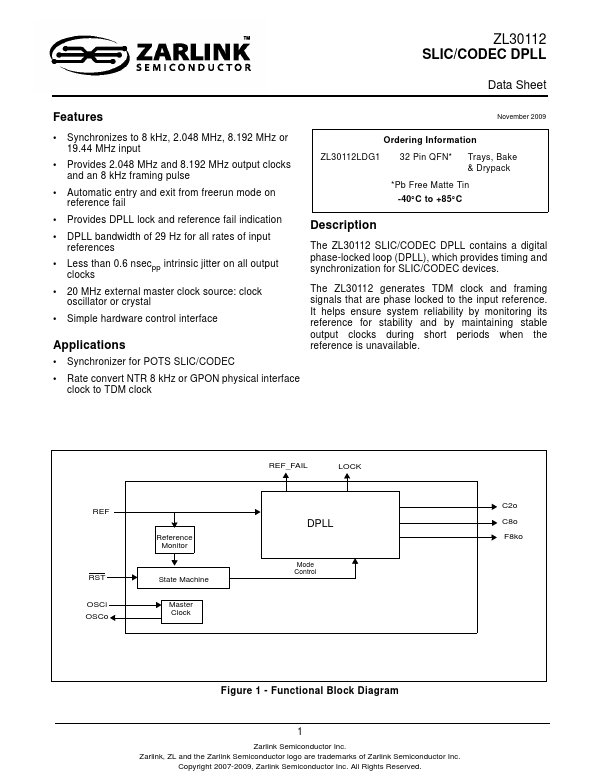

Description

The ZL30112 SLIC/CODEC...