ZL30117

ZL30117 is SONET/SDH Low Jitter Line Card Synchronizer manufactured by Zarlink Semiconductor.

Features

- Synchronizes with standard tele system references and synthesizes a wide variety of protected tele line interface clocks that are pliant with Telcordia GR-253-CORE and ITU-T G.813 Internal APLL provides standard output clock frequencies from 6.48 MHz up to 622.08 MHz with jitter less than 1 ps RMS for OC-48/STM-16 interfaces Programmable output synthesizer generates clock frequencies from any multiple of 8 k Hz up to 77.76 MHz in addition to 2 k Hz Digital Phase Locked-Loop (DPLL) provides all the features necessary for generating SONET/SDH pliant clocks including automatic hitless reference switching, automatic mode selection (locked, free-run, holdover), and selectable loop bandwidth

- -

- -

- -

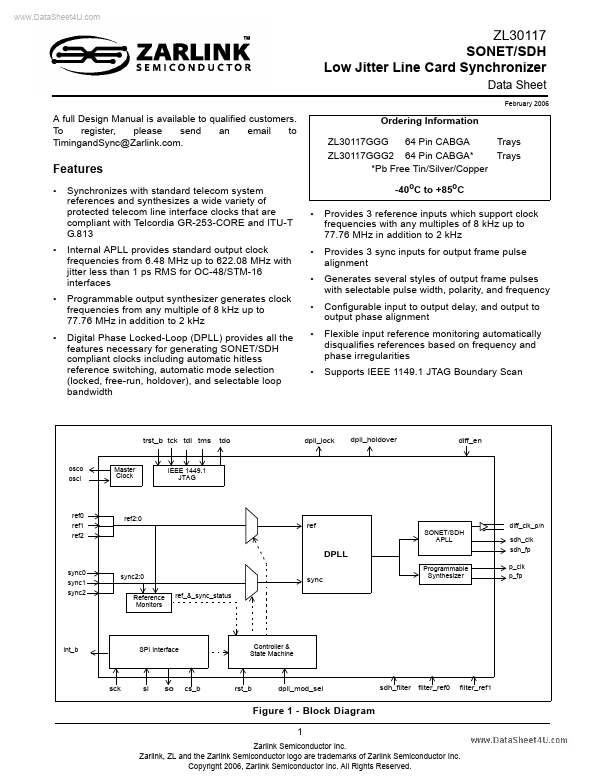

- - trst_b tck tdi tms tdo dpll_lock dpll_holdover diff_en osco osci

Master Clock

IEEE 1449.1 JTAG ref0 ref1 ref2 ref2:0 ref diff_clk_p/n SONET/SDH APLL sdh_clk sdh_fp p_clk p_fp

DPLL sync0 sync1 sync2 sync2:0 Reference Monitors ref_&_sync_status sync

Programmable Synthesizer int_b

SPI Interface

Controller & State Machine sck si so cs_b rst_b dpll_mod_sel sdh_filter filter_ref0 filter_ref1

Figure 1

- Block Diagram 1

Zarlink Semiconductor Inc. Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc. Copyright 2006, Zarlink Semiconductor Inc. All Rights Reserved.

..

Applications

- -

- -

- - AMCs for Advanced TCATM and Micro TCA Systems Multi-Service Edge Switches or Routers DSLAM Line Cards WAN Line Cards RNC/Mobile Switching Center Line Cards ADM Line Cards

Data Sheet

Zarlink Semiconductor Inc.

..

ZL30117 Table of Contents

Data Sheet

1.0 Functional Description

- -

- -

- -

- -

- -

- -

- . 9 1.1 DPLL Features

- -

- -

- -

- -

- -

-...