ZL30119

ZL30119 is Low Jitter Line Card Synchronizer manufactured by Zarlink Semiconductor.

Features

Ordering Information

June 2006

- Synchronizes with standard tele system references and synthesizes a wide variety of protected tele line interface clocks that are pliant with Telcordia GR-253-CORE and ITU-T G.813

- Internal APLL provides standard output clock frequencies up to 622.08 MHz that meet jitter requirements for interfaces up to OC-192/STM-64

- Programmable output synthesizers (P0, P1) generate clock frequencies from any multiple of 8 k Hz up to 77.76 MHz in addition to 2 k Hz

- Provides two DPLLs which are independently configurable through a serial peripheral interface

- DPLL1 provides all the features necessary for generating SONET/SDH pliant clocks including automatic hitless reference switching, automatic mode selection (locked, free-run, holdover), and selectable loop bandwidth

- DPLL2 provides a prehensive set of features for generating derived output clocks and other general purpose clocks

ZL30119GGG 100 Pin CABGA Trays ZL30119GGG2 100 Pin CABGA- Trays

- Pb Free Tin/Silver/Copper

-40o C to +85o C

- Provides 8 reference inputs which support clock frequencies with any multiples of 8 k Hz up to 77.76 MHz in addition to 2 k Hz

- Provides 3 sync inputs for output frame pulse alignment

- Generates several styles of output frame pulses with selectable pulse width, polarity, and frequency

- Configurable input to output delay, and output to output phase alignment

- Flexible input reference monitoring automatically disqualifies references based on frequency and phase irregularities

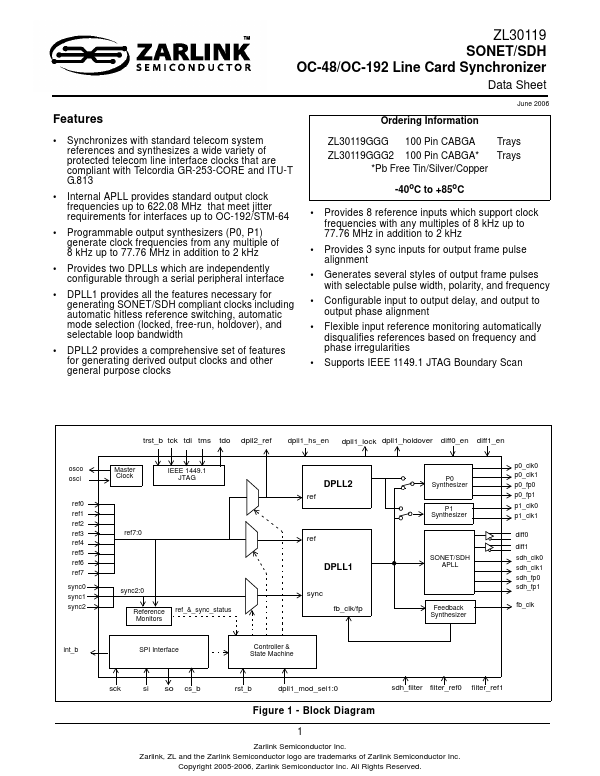

- Supports IEEE 1149.1 JTAG Boundary Scan osco osci ref0 ref1 ref2 ref3 ref4 ref5 ref6 ref7 sync0 sync1 sync2 int_b trst_b tck tdi tms tdo dpll2_ref dpll1_hs_en dpll1_lock dpll1_holdover diff0_en diff1_en

Master Clock

IEEE 1449.1 JTAG ref7:0 sync2:0

Reference ref_&_sync_status Monitors

DPLL2 ref ref

DPLL1 sync fb_clk/fp

P0 Synthesizer

P1 Synthesizer

SONET/SDH APLL

Feedback Synthesizer p0_clk0 p0_clk1 p0_fp0 p0_fp1 p1_clk0 p1_clk1 diff0 diff1 sdh_clk0 sdh_clk1...