SN65LVDS305 Overview

Key Specifications

Package: BGA

Pins: 80

Operating Voltage: 1.8 V

Height: 1 mm

Description

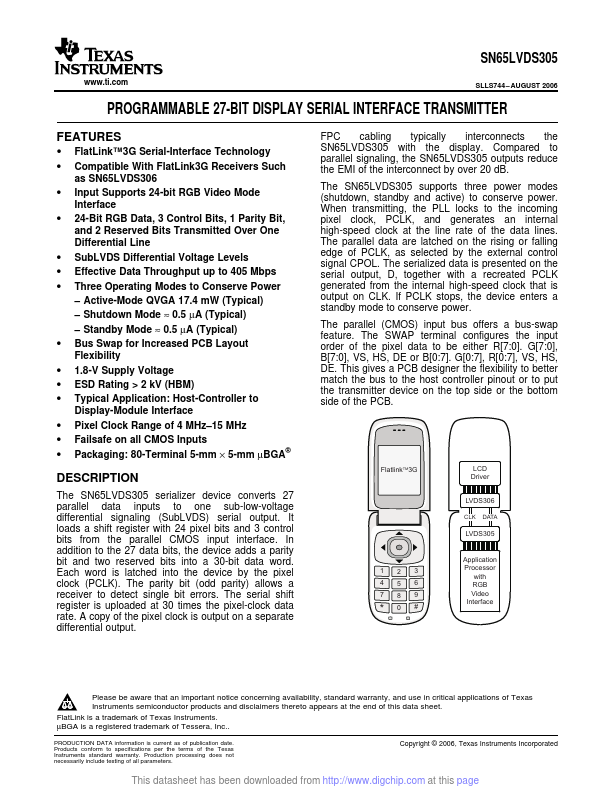

The SN65LVDS305 serializer device converts 27 parallel data inputs to one sub-low-voltage differential signaling (SubLVDS) serial output. It loads a shift register with 24 pixel bits and 3 control bits from the parallel CMOS input interface.

Key Features

- FlatLink™3G Serial-Interface Technology

- Compatible With FlatLink3G Receivers Such as SN65LVDS306

- Input Supports 24-bit RGB Video Mode Interface

- 24-Bit RGB Data, 3 Control Bits, 1 Parity Bit, and 2 Reserved Bits Transmitted Over One Differential Line

- SubLVDS Differential Voltage Levels