CY7C1041BN

Overview

- Temperature range: ❐ Commercial: 0 °C to 70 °C ❐ Automotive-A: -40 °C to 85 °C

- High speed ❐ tAA = 15 ns

- Low active power

- Low CMOS standby power ❐ 2.75 mW (max.)

- 2.0 V data retention (400 W at 2.0 V retention)

- Automatic power-down when deselected

- TTL-compatible inputs and outputs

- Easy memory expansion with CE and OE features

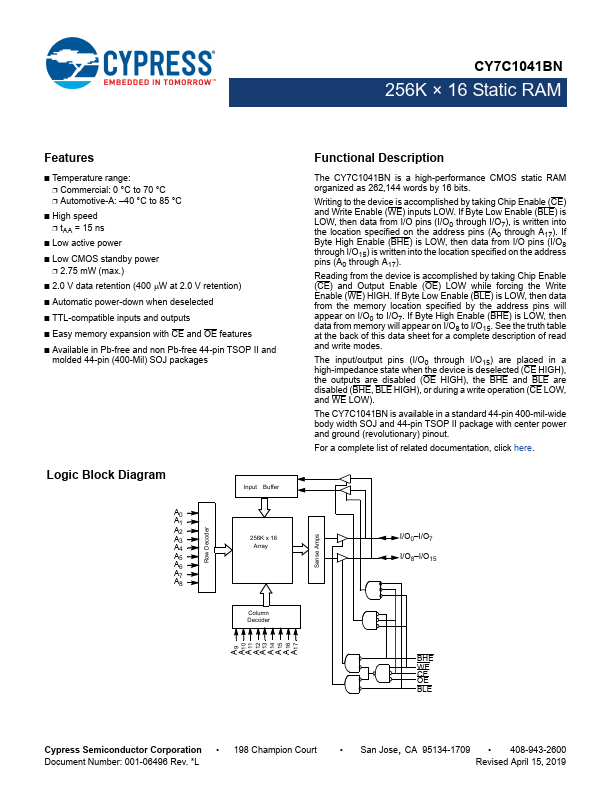

- Available in Pb-free and non Pb-free 44-pin TSOP II and molded 44-pin (400-Mil) SOJ packages Logic Block Diagram