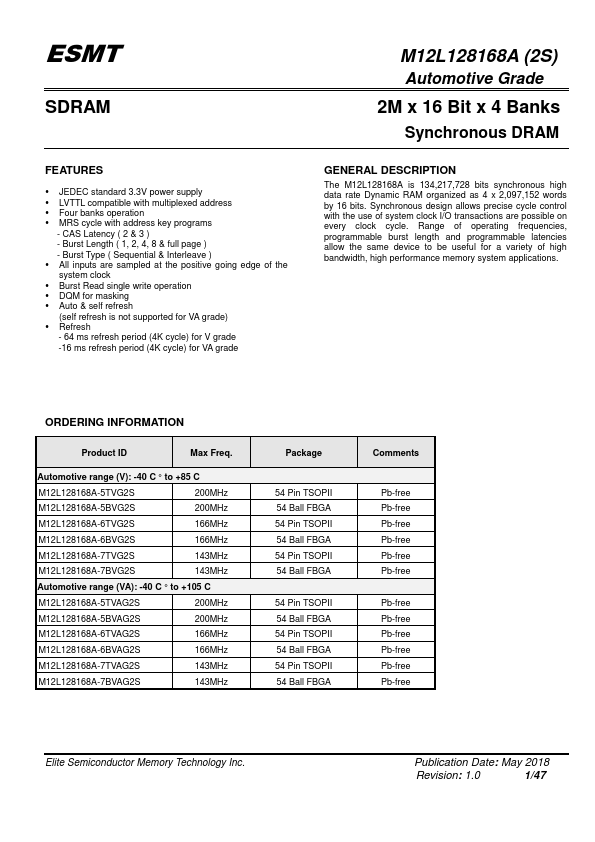

M12L128168A-7BVAG2S

Overview

The M12L128168A is 134,217,728 bits synchronous high data rate Dynamic RAM organized as 4 x 2,097,152 words by 16 bits. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle.

- JEDEC standard 3.3V power supply

- LVTTL compatible with multiplexed address

- Four banks operation

- MRS cycle with address key programs - CAS Latency ( 2 & 3 ) - Burst Length ( 1, 2, 4, 8 & full page ) - Burst Type ( Sequential & Interleave )

- All inputs are sampled at the positive going edge of the system clock

- Burst Read single write operation

- DQM for masking

- Auto & self refresh (self refresh is not supported for VA grade)

- Refresh - 64 ms refresh period (4K cycle) for V grade -16 ms refresh period (4K cycle) for VA grade