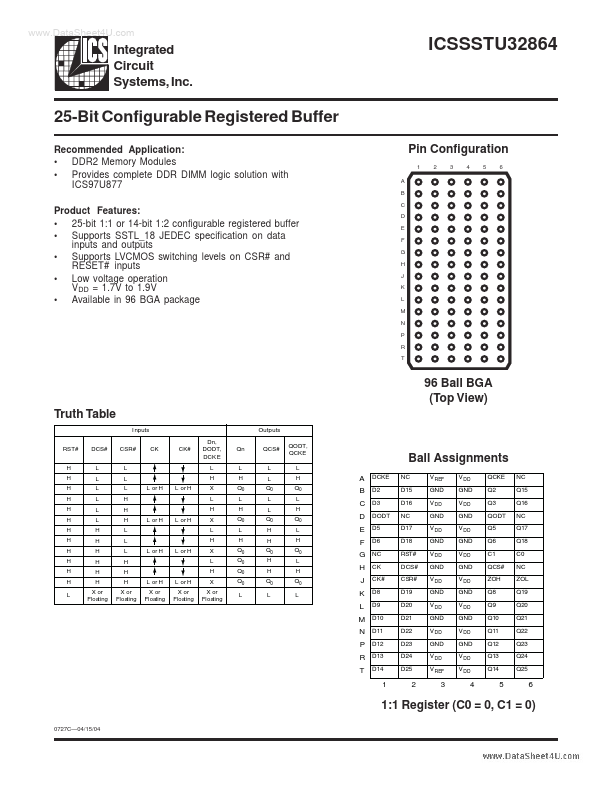

ICSSSTU32864 Description

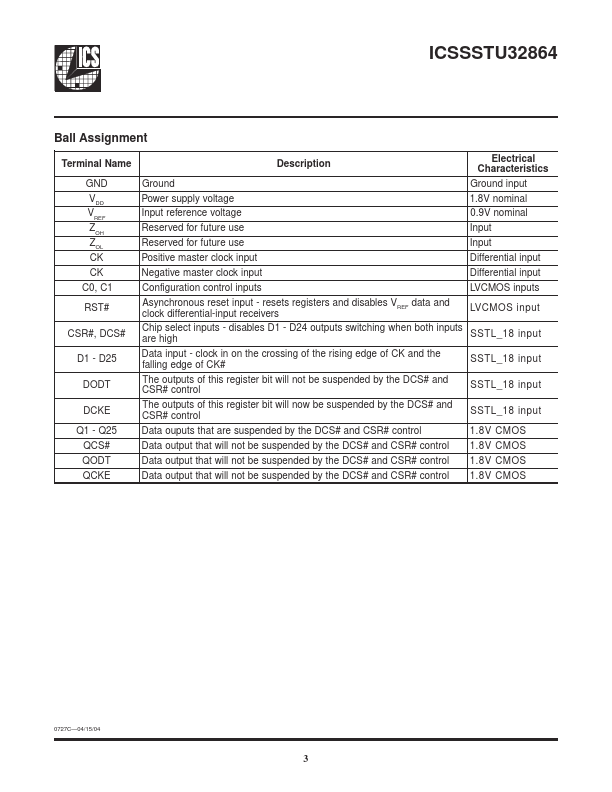

All clock and data inputs are patible with the JEDEC standard for SSTL_18. The control inputs are LVCMOS. All outputs are 1.8-V CMOS drivers that have been optimized to drive the DDR-II DIMM load.

ICSSSTU32864 Key Features

- 25-bit 1:1 or 14-bit 1:2 configurable registered buffer

- Supports SSTL_18 JEDEC specification on data inputs and outputs

- Supports LVCMOS switching levels on CSR# and RESET# inputs

- Low voltage operation VDD = 1.7V to 1.9V

- Available in 96 BGA package