DS99R104

DS99R104 is DC-Balanced 24-Bit LVDS Serializer and Deserializer manufactured by National Semiconductor.

- Part of the DS99R103 comparator family.

- Part of the DS99R103 comparator family.

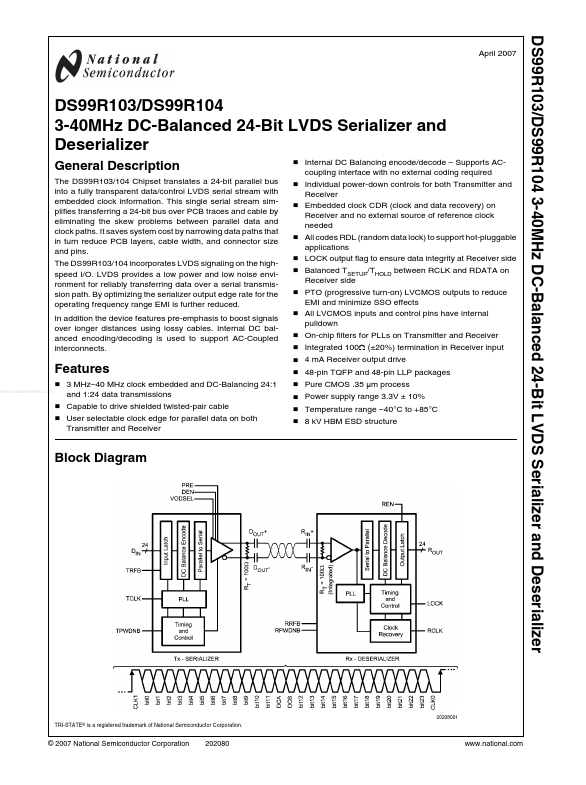

DS99R103/DS99R104 3-40MHz DC-Balanced 24-Bit LVDS Serializer and Deserializer

April 2007

DS99R103/DS99R104 3-40MHz DC-Balanced 24-Bit LVDS Serializer and Deserializer

General Description

The DS99R103/104 Chipset translates a 24-bit parallel bus into a fully transparent data/control LVDS serial stream with embedded clock information. This single serial stream simplifies transferring a 24-bit bus over PCB traces and cable by eliminating the skew problems between parallel data and clock paths. It saves system cost by narrowing data paths that in turn reduce PCB layers, cable width, and connector size and pins. The DS99R103/104 incorporates LVDS signaling on the highspeed I/O. LVDS provides...