uPD46185364B Description

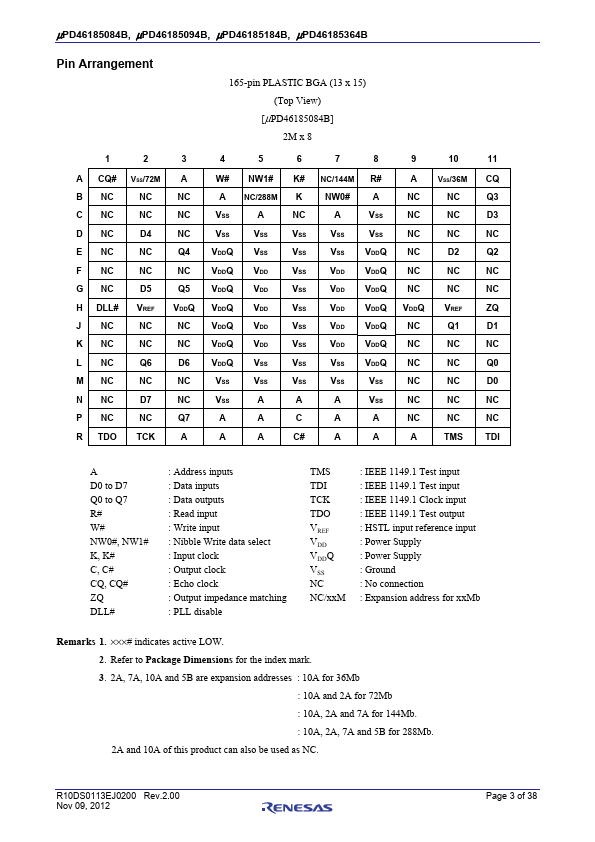

The μPD46185084B, μPD46185094B, μPD46185184B and μPD46185364B integrate unique synchronous peripheral circuitry and a burst counter. All input registers controlled by an input clock pair (K and K#) are latched on the positive edge of K and K#. These products are suitable for application which require synchronous operation, high speed, low voltage, high density and wide bit configuration.

uPD46185364B Key Features

- 1.8 ± 0.1 V power supply

- 165-pin PLASTIC BGA (13 x 15)

- HSTL interface

- PLL circuitry for wide output data valid window and future frequency scaling

- Separate independent read and write data ports with concurrent transactions

- 100% bus utilization DDR READ and WRITE operation

- Four-tick burst for reduced address frequency

- Two input clocks (K and K#) for precise DDR timing at clock rising edges only

- Two output clocks (C and C#) for precise flight time

- Internally self-timed write control