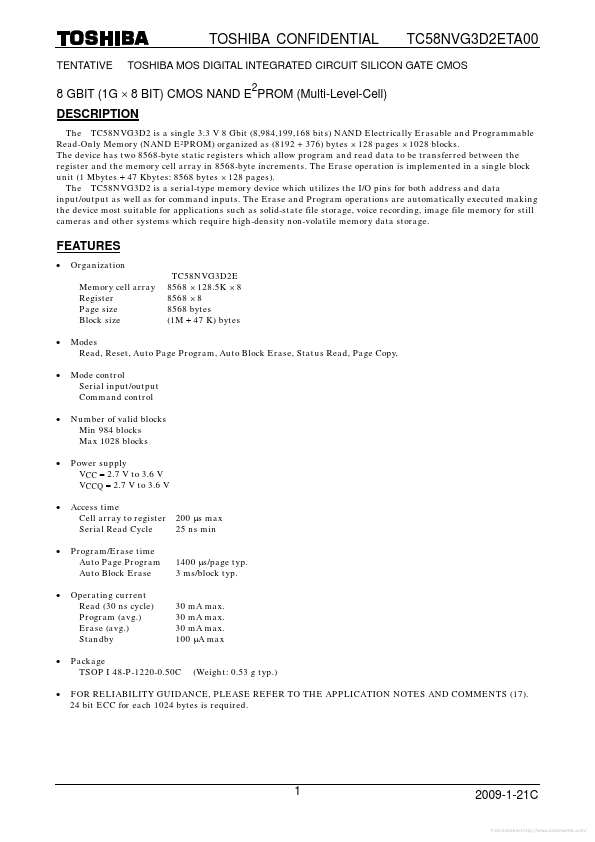

| Part | TC58NVG3D2ETA00 |

|---|---|

| Description | 8 GBIT (1G X 8 BIT) CMOS NAND E2PROM |

| Manufacturer | Toshiba |

| Size | 482.59 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| TC58BVG0S3HTA00 | Toshiba | 1 GBIT (128M x 8 BIT) CMOS NAND E2PROM |

| TC58NVG1S3HTA00 | Toshiba | 2 GBIT (256M x 8 BIT) CMOS NAND E2PROM |

| CAT93C66 | Catalyst Semiconductor | 1K/2K/2K/4K/16K-Bit Microwire Serial E2PROM |