Datasheet Summary

..

White Electronic Designs

512K x 32/256K x 32 Dual Array Synchronous Pipeline Burst NBL SRAM

Features

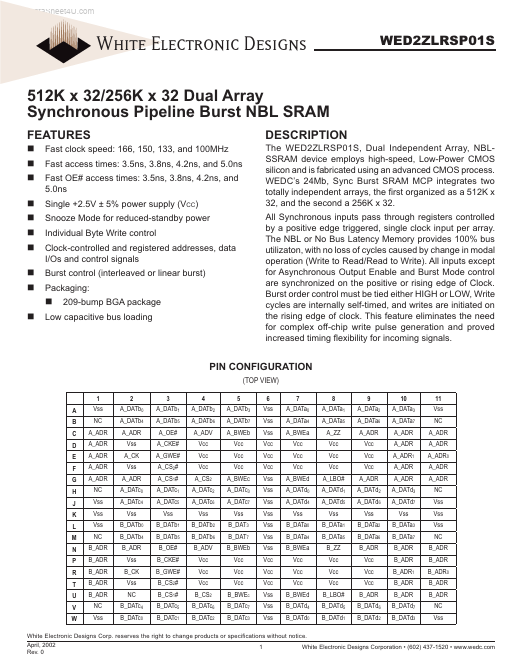

Fast clock speed: 166, 150, 133, and 100MHz Fast access times: 3.5ns, 3.8ns, 4.2ns, and 5.0ns Fast OE# access times: 3.5ns, 3.8ns, 4.2ns, and 5.0ns Single +2.5V ± 5% power supply (VCC) Snooze Mode for reduced-standby power Individual Byte Write control Clock-controlled and registered addresses, data I/Os and control signals Burst control (interleaved or linear burst) Packaging: 209-bump BGA package Low capacitive bus loading

DESCRIPTION

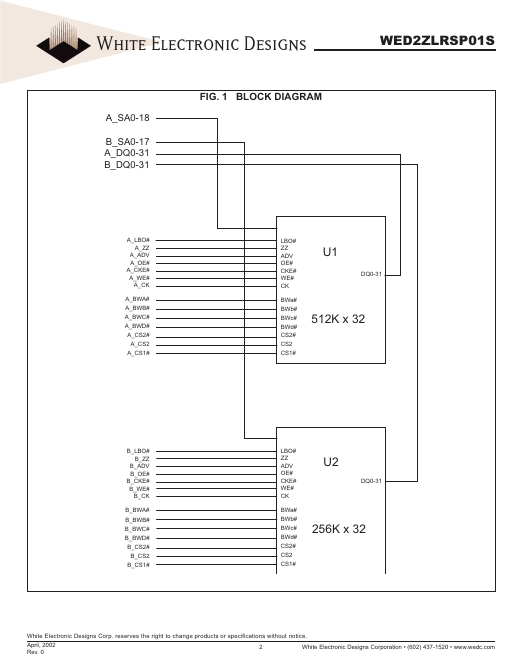

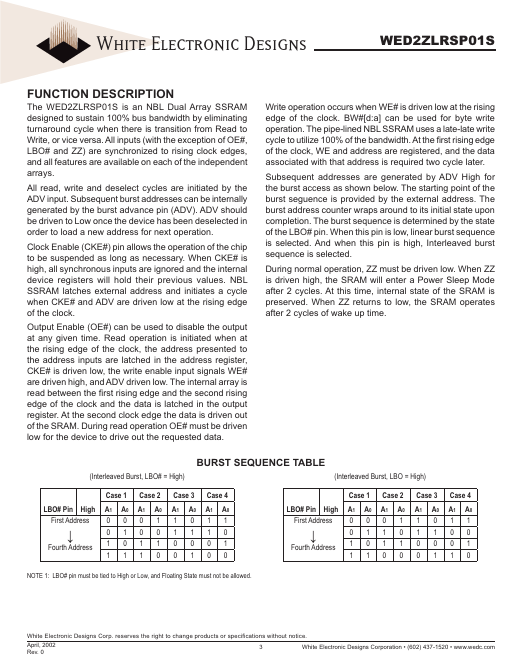

The WED2ZLRSP01S, Dual Independent Array, NBLSSRAM device employs high-speed, Low-Power CMOS silicon and is fabricated...