ZL30110

Description

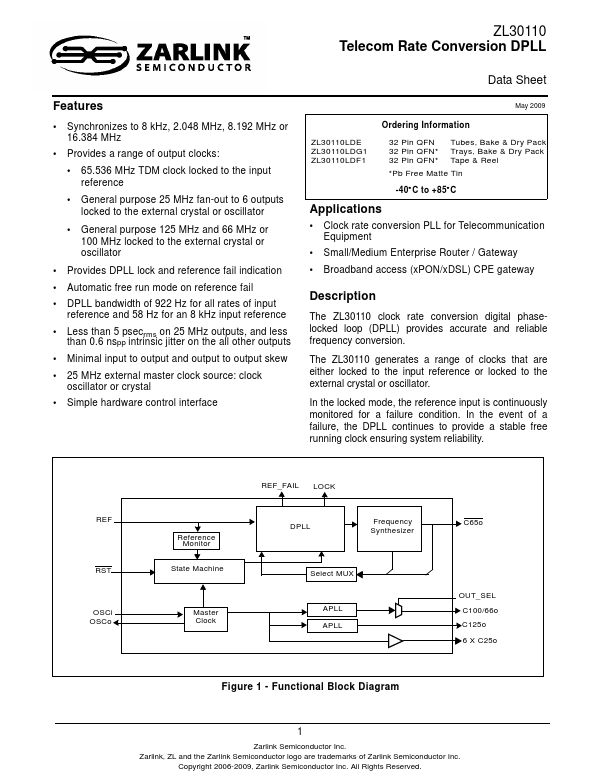

The ZL30110 clock rate conversion digital phaselocked loop (DPLL) provides accurate and reliable frequency conversion. The ZL30110 generates a range of clocks that are either locked to the input reference or locked to the external crystal or oscillator.

Key Features

- Synchronizes to 8 kHz, 2.048 MHz, 8.192 MHz or 16.384 MHz

- Provides a range of output clocks

- 65.536 MHz TDM clock locked to the input reference

- General purpose 25 MHz fan-out to 6 outputs locked to the external crystal or oscillator

- General purpose 125 MHz and 66 MHz or 100 MHz locked to the external crystal or oscillator

- Provides DPLL lock and reference fail indication

- Automatic free run mode on reference fail

- DPLL bandwidth of 922 Hz for all rates of input reference and 58 Hz for an 8 kHz input reference

- Less than 5 psecrms on 25 MHz outputs, and less than 0.6 nspp intrinsic jitter on the all other outputs

- Minimal input to output and output to output skew