Description

- JEDEC Standard

Symbol

Type

Function

CK, CK# CKE

CS# ODT RAS#.CAS#.WE# DM, (DMU), (DML) BA0 - BA2 A0 - A14

A10 / AP

A12 / BC# RESET#

DQ( DQL, DQU)

Input Input

Input Input Input

Clock: CK and CK# are differential clock inputs.All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of CK#.Clock Enable: CKE HIGH activates, and CKE Low deactivates, internal clock signals and device input buffers and output drivers.Taking CKE Low prov

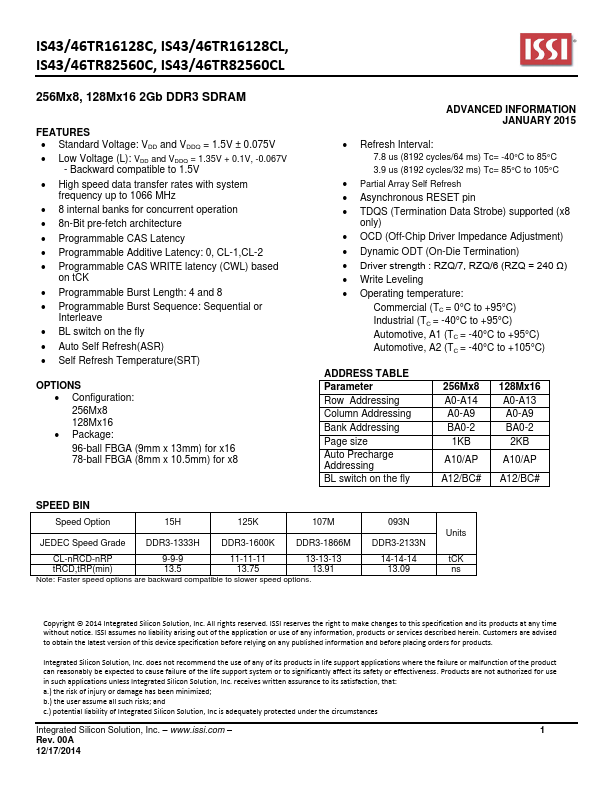

Features

- Standard Voltage: VDD and VDDQ = 1.5V ± 0.075V.

- Low Voltage (L): VDD and VDDQ = 1.35V + 0.1V, -0.067V

- Backward compatible to 1.5V.

- High speed data transfer rates with system

frequency up to 1066 MHz.

- 8 internal banks for concurrent operation.

- 8n-Bit pre-fetch architecture.

- Programmable CAS Latency.

- Programmable Additive Latency: 0, CL-1,CL-2.

- Programmable CAS WRITE latency (CWL) based

on tCK.

- Programmable Burst Length: 4 and 8.

- Programmable Bu.