Description

The 128Mb DDR SDRAM is a high-speed CMOS, dynamic random-access memory containing 134,217,728 bits.

Features

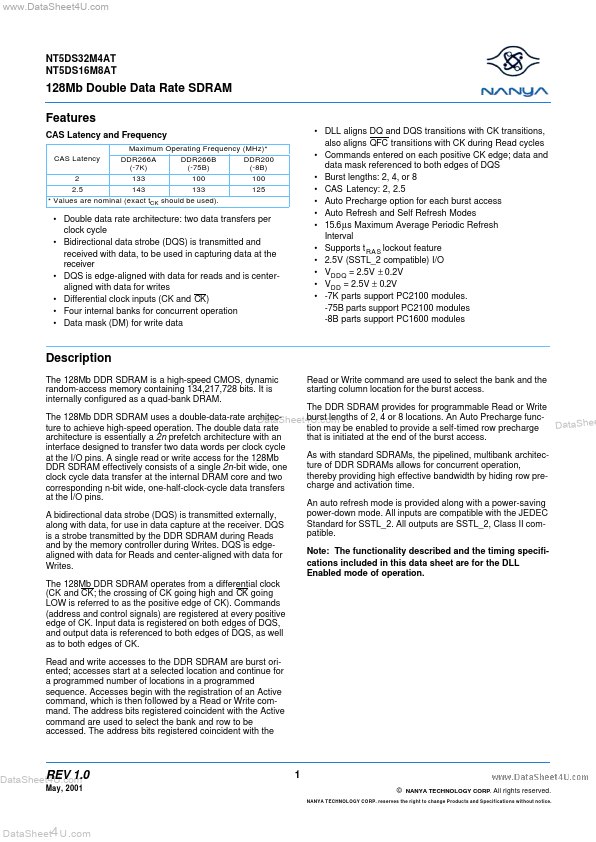

- CAS Latency and Frequency

Maximum Operating Frequency (MHz).

- DDR266A DDR266B DDR200 (-7K) (-75B) (-8B) 2 133 100 100 2.5 143 133 125.

- Values are nominal (exact tCK should be used). CAS Latency.

- Double data rate architecture: two data transfers per clock cycle.

- Bidirectional data strobe (DQS) is transmitted and received with data, to be used in capturing data at the receiver.

- DQS is edge-aligned with data for reads and is centeraligned with data for writes.