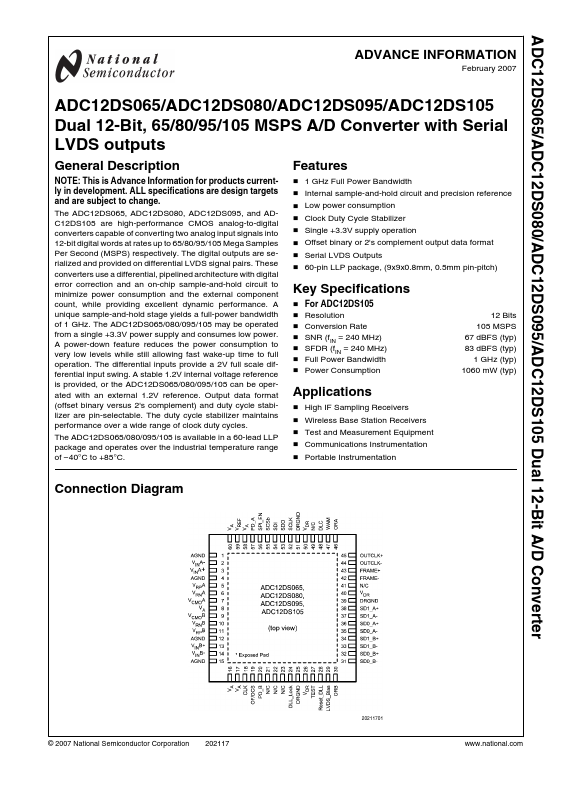

Description

NOTE: This is Advance Information for products currently in development.

Features

- 1 GHz Full Power Bandwidth Internal sample-and-hold circuit and precision reference Low power consumption Clock Duty Cycle Stabilizer Single +3.3V supply operation Offset binary or 2's complement output data format Serial LVDS Outputs 60-pin LLP package, (9x9x0.8mm, 0.5mm pin-pitch)

Key Specifications.

- For ADC12DS105 Resolution Conversion Rate SNR (fIN = 240 MHz) SFDR (fIN = 240 MHz) Full Power Bandwidth Po.