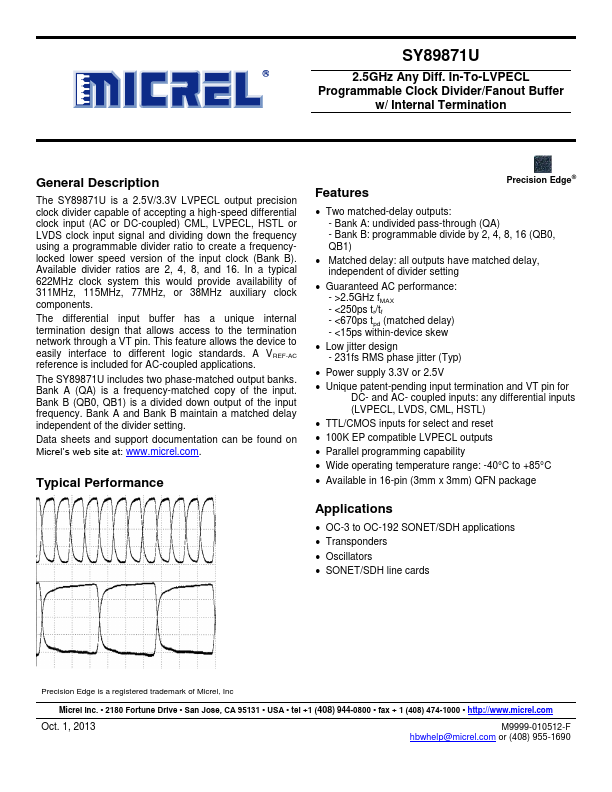

SY89871U Overview

Description

The SY89871U is a 2.5V/3.3V LVPECL output precision clock divider capable of accepting a high-speed differential clock input (AC or DC-coupled) CML, LVPECL, HSTL or LVDS clock input signal and dividing down the frequency using a programmable divider ratio to create a frequencylocked lower speed version of the input clock (Bank B). Available divider ratios are 2, 4, 8, and 16.

Key Features

- Two matched-delay outputs

- Bank A: undivided pass-through (QA)

- Bank B: programmable divide by 2, 4, 8, 16 (QB0, QB1)

- Matched delay: all outputs have matched delay, independent of divider setting

- Guaranteed AC performance

- >2.5GHz fMAX

- <250ps tr/tf

- <670ps tpd (matched delay)

- <15ps within-device skew

- Low jitter design