Datasheet Summary

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Low Voltage PLL Clock Driver

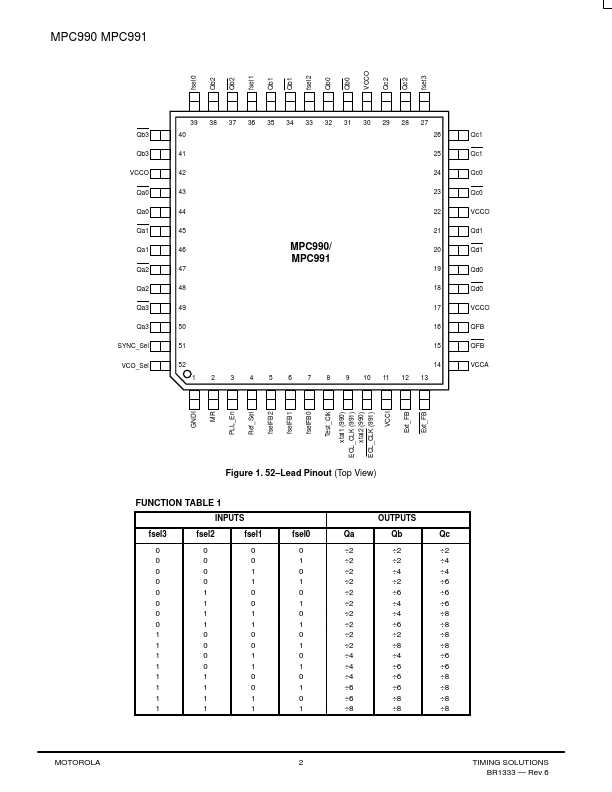

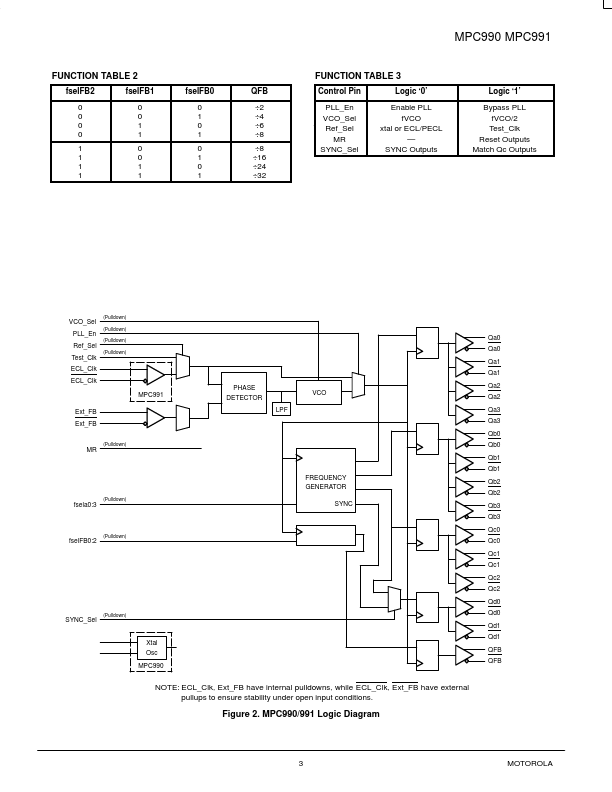

The MPC990/991 is a 3.3V patible, PLL based ECL/PECL clock driver. The fully differential design ensures optimum skew and PLL jitter performance. The performance of the MPC990/991 makes the device ideal for Workstation, Mainframe puter and Telemunication applications. The MPC990 and MPC991 devices are identical except in the interface to the reference clock for the PLL. The MPC990 offers an on- board crystal oscillator as the PLL reference while the MPC991 offers a differential ECL/PECL input for applications which need to lock to an existing clock signal. Both designs offer a secondary single- ended ECL clock for...