Datasheet Summary

MOTOROLA

Freescale SEMICONDUCTOR TECHNICAL DATA Semiconductor, Inc.

Order Number: MPC99J93/D Rev 1, 08/2003

Product Preview Intelligent Dynamic Clock Switch (IDCS) PLL Clock Driver

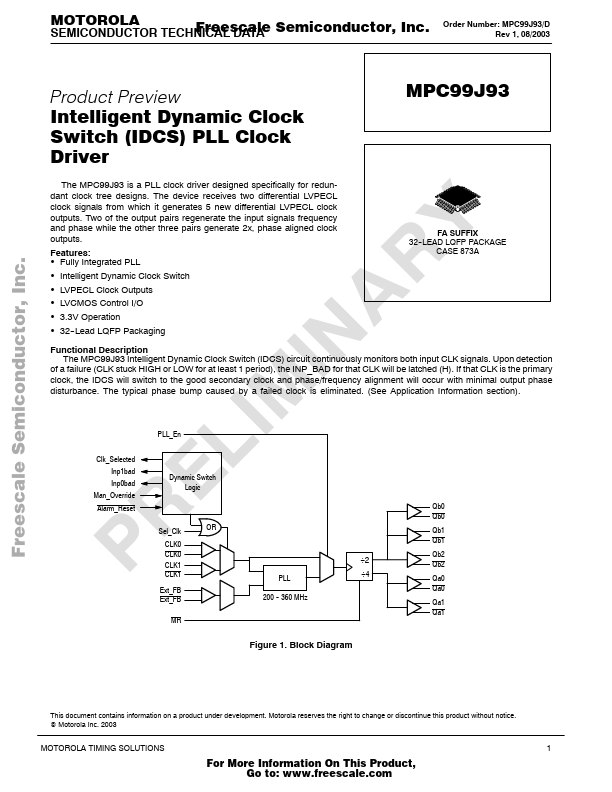

The MPC99J93 is a PLL clock driver designed specifically for redundant clock tree designs. The device receives two differential LVPECL clock signals from which it generates 5 new differential LVPECL clock outputs. Two of the output pairs regenerate the input signals frequency and phase while the other three pairs generate 2x, phase aligned clock outputs. Features

:

- Fully Integrated PLL

Freescale Semiconductor, Inc...

FA SUFFIX 32--LEAD LQFP PACKAGE CASE 873A

- -

- -

- Intelligent Dynamic Clock...