Datasheet Summary

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

U 4 tPLL Clock Driver Low Voltage e e h S a at .D w w w-

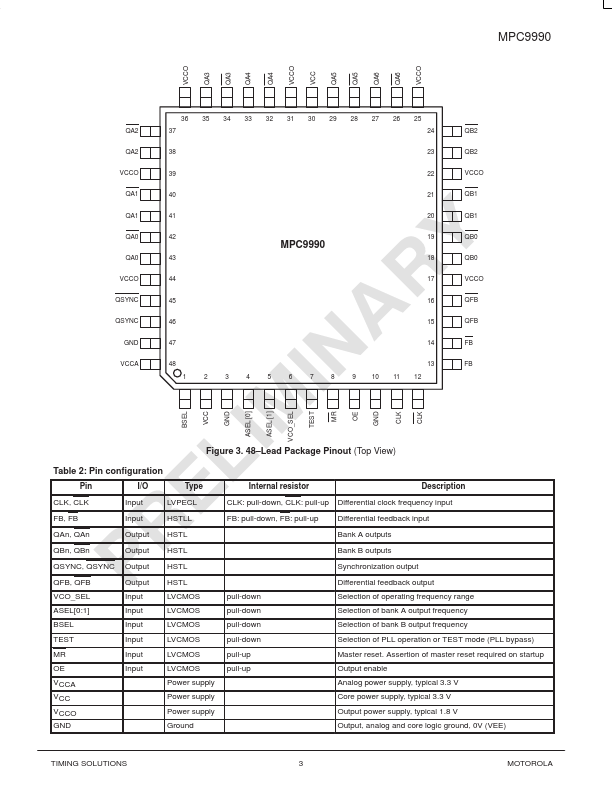

Supports high performance HSTL clock distribution systems patible to IA64 processor systems Fully Integrated PLL, differential design Core logic operates from 3.3 V power supply HSTL outputs operate from a 1.8 V supply Programmable frequency by output bank 10 HSTL patible outputs (two banks) HSTL patible PLL feedback output HSTL patible sychronization output (QSYNC) Max. skew of 80 ps within output bank Zero- delay capability: max. SPO (tpd) window of 150 ps Temperature range of 0 to +70°C

Product Preview m o .c

Order Number: MPC9990/D Rev 4, 01/2002

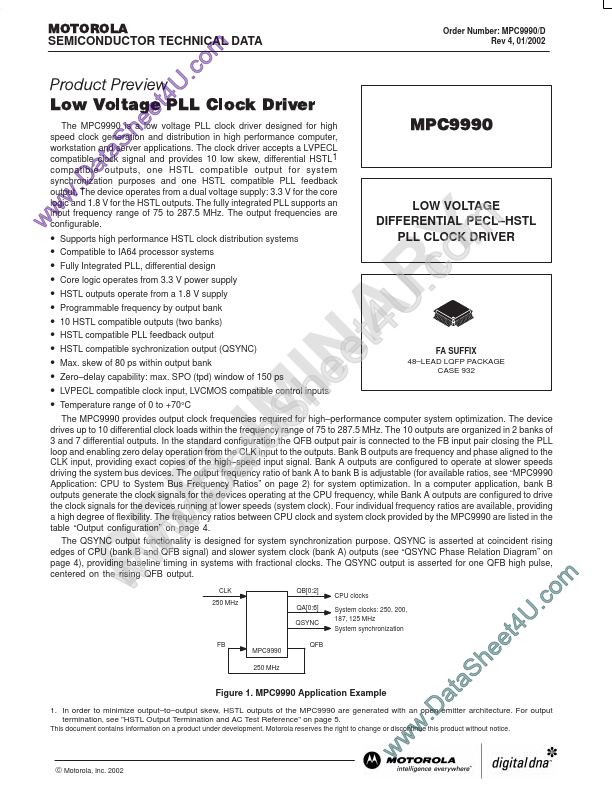

The MPC9990 is a low voltage...