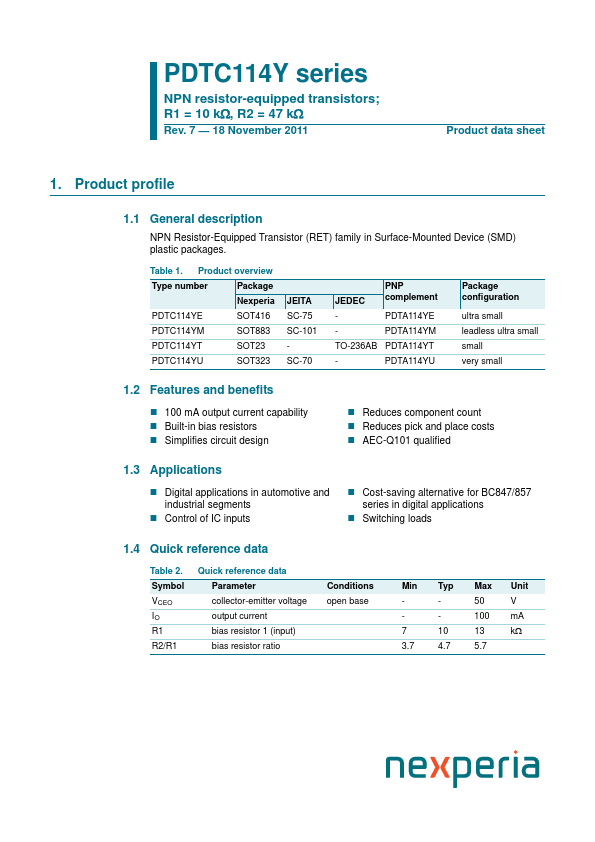

PDTC114YU

FEATURES

- Built-in bias resistors R1 and R2 (typ. 10 kΩ and 47 kΩ respectively)

- Simplification of circuit design

- Reduces number of ponents and board space. APPLICATIONS

- Especially suitable for space reduction in interface and driver circuits

- Inverter circuit configurations without use of external resistors. DESCRIPTION

NPN resistor-equipped transistor in an SC-70 (SOT323) plastic package. PINNING

MGA893

- 1

PDTC114YU handbook, 4 columns

3 3 R1 1 R2 2 1 Top view 2

MAM134

Fig.1 Simplified outline (SC-70; SOT323) and symbol.

MARKING TYPE NUMBER

1 2 3

MARKING CODE(1) ∗30

PDTC114YU Note

PIN 1 2 3

DESCRIPTION base/input emitter/ground collector/output Fig.2 Equivalent inverter symbol.

1. ∗ = -: Made in Hong Kong. ∗ = t: Made in Malaysia.

LIMITING VALUES In accordance with the Absolute Maximum Rating System (IEC 134). SYMBOL VCBO VCEO VEBO VI PARAMETER collector-base voltage collector-emitter voltage emitter-base voltage input voltage positive negative IO ICM Ptot Tstg Tj...