CY2DP1510

Key Features

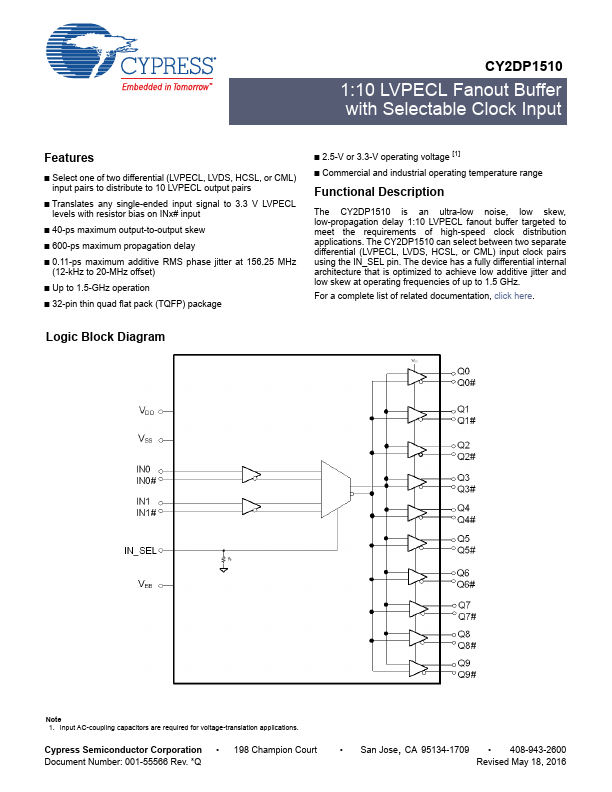

- Select one of two differential (LVPECL, LVDS, HCSL, or CML) input pairs to distribute to 10 LVPECL output pairs

- Translates any single-ended input signal to 3.3 V LVPECL levels with resistor bias on INx# input

- 40-ps maximum output-to-output skew

- 600-ps maximum propagation delay

- 0.11-ps maximum additive RMS phase jitter at 156.25 MHz

- Up to 1.5-GHz operation

- 32-pin thin quad flat pack (TQFP) package

- mercial and industrial operating temperature range