Datasheet Summary

..

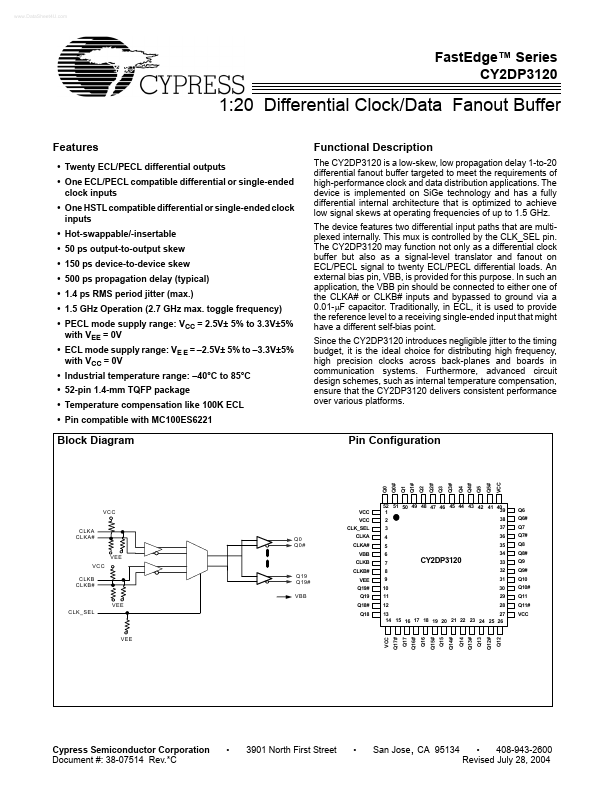

FastEdge™ Series CY2DP3120

1:20 Differential Clock/Data Fanout Buffer

Features

- Twenty ECL/PECL differential outputs

- One ECL/PECL patible differential or single-ended clock inputs

- One HSTL patible differential or single-ended clock inputs

- Hot-swappable/-insertable

- 50 ps output-to-output skew

- 150 ps device-to-device skew

- 500 ps propagation delay (typical)

- 1.4 ps RMS period jitter (max.)

- 1.5 GHz Operation (2.7 GHz max. toggle frequency)

- PECL mode supply range: VCC = 2.5V± 5% to 3.3V±5% with VEE = 0V

- ECL mode supply range: VE E =

- 2.5V± 5% to

- 3.3V±5% with VCC = 0V

- Industrial temperature range:

- 40°C to 85°C

- 52-pin 1.4-mm TQFP package

-...