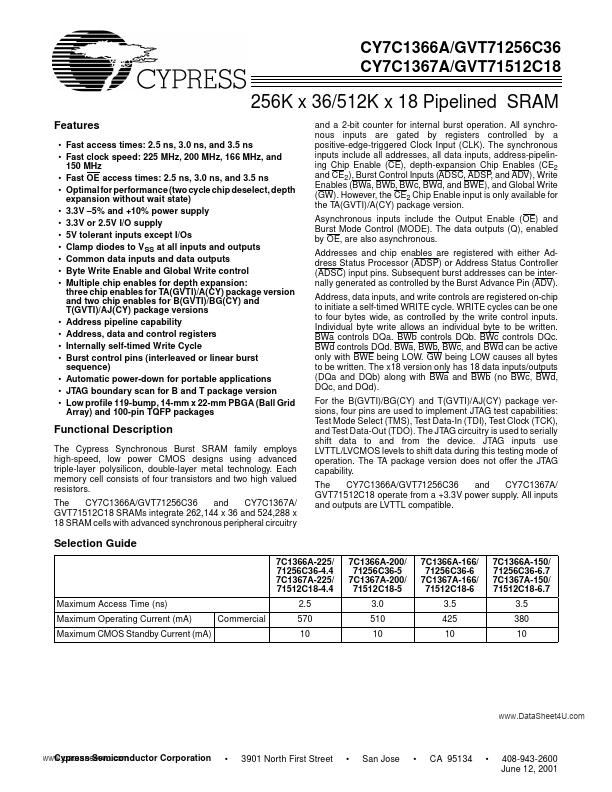

GVT71256C36 Overview

Key Specifications

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.63 V

Min Voltage (typical range): 3.135 V

Max Frequency: 200 MHz

Key Features

- Fast access times: 2.5 ns, 3.0 ns, and 3.5 ns

- Fast clock speed: 225 MHz, 200 MHz, 166 MHz, and 150 MHz

- Fast OE access times: 2.5 ns, 3.0 ns, and 3.5 ns

- Optimal for performance (two cycle chip deselect, depth expansion without wait state)

- 3.3V –5% and +10% power supply