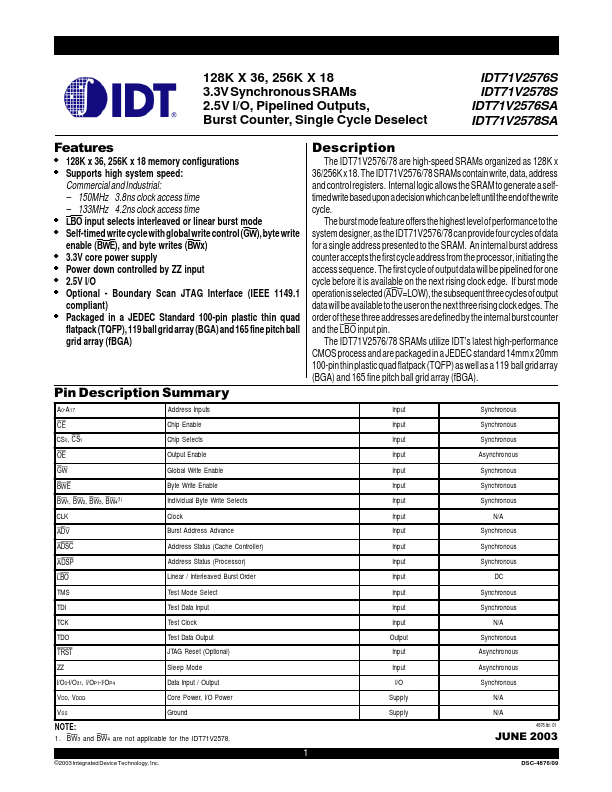

Part number:

IDT71V2576SA, IDT-71V

Manufacturer:

Integrated Device Technology

File Size:

282.49 KB

Description:

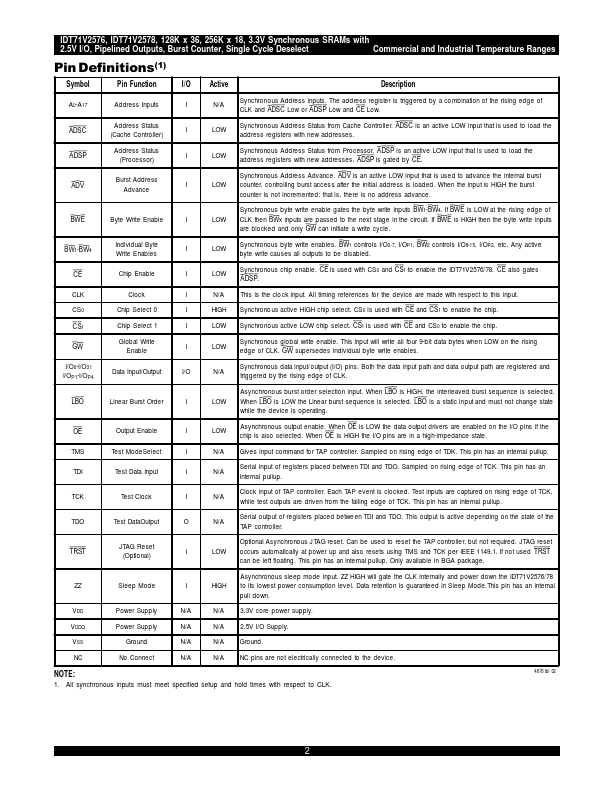

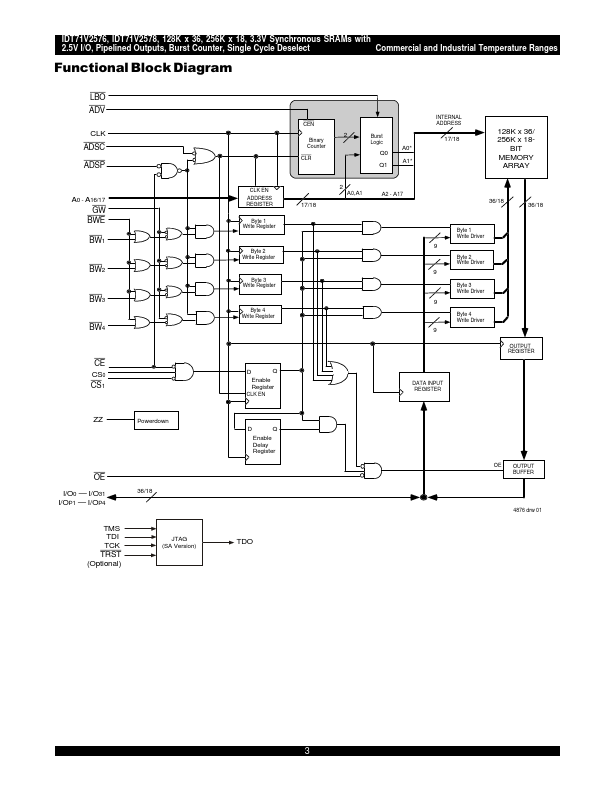

128k x 36/ 256k x 18 3.3v synchronous srams 2.5v i/o/ pipelined outputs/ burst counter/ single cycle deselect.

Note:

This datasheet PDF includes multiple part numbers: IDT71V2576SA, IDT-71V.

Please refer to the document for exact specifications by model.