PLL205-04

PLL205-04 is Programmable Clock Generator manufactured by PhaseLink.

m Preliminary PLL205-04 o c . Programmable Clock Generator for VIA KT-266 Chipset U 4 t e Features

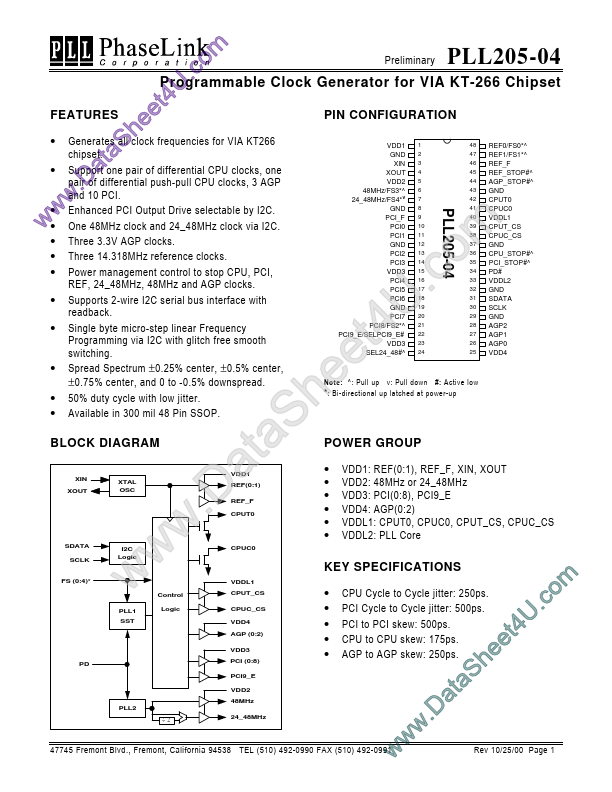

PIN CONFIGURATION e h

- Generates all clock frequencies for VIA KT266 S chipset. a t

- Support one pair of differential CPU clocks, one a pair of differential push-pull CPU clocks, 3 AGP .D and 10 PCI. w

- w Enhanced PCI Output Drive selectable by I2C. w- One 48MHz clock and 24_48MHz clock via I2C.

- -

- -

- -

- - Three 3.3V AGP clocks. Three 14.318MHz reference clocks. Power management control to stop CPU, PCI, REF, 24_48MHz, 48MHz and AGP clocks. Supports 2-wire I2C serial bus interface with readback. Single byte micro-step linear Frequency Programming via I2C with glitch free smooth...