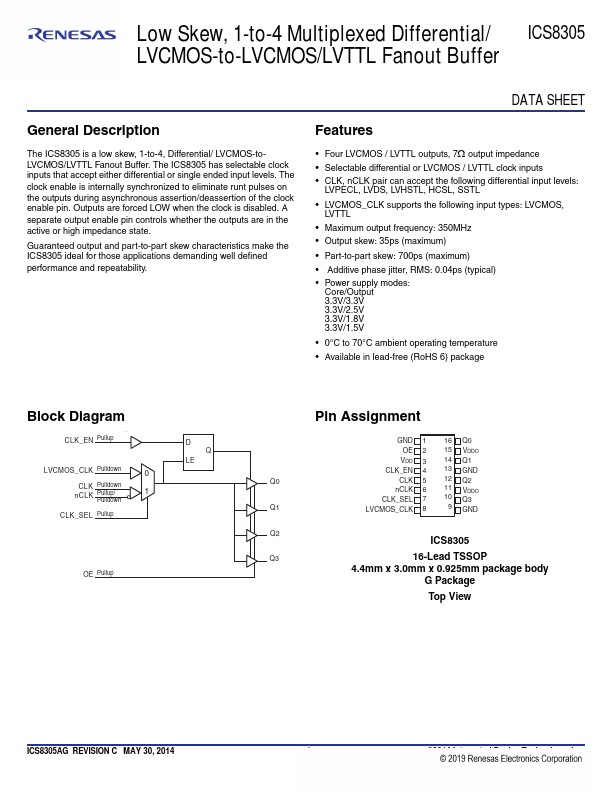

ICS8305 Overview

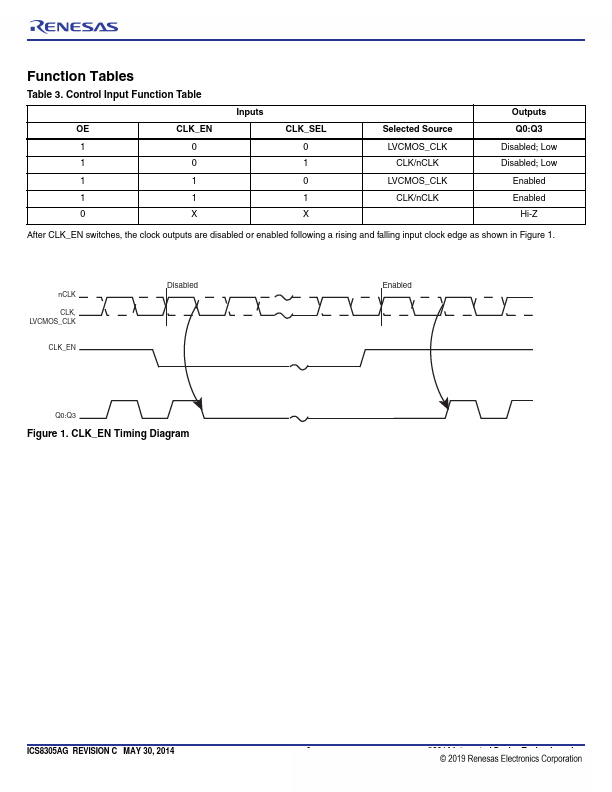

The ICS8305 is a low skew, 1-to-4, Differential/ LVCMOS-toLVCMOS/LVTTL Fanout Buffer. The ICS8305 has selectable clock inputs that accept either differential or single ended input levels. The clock enable is internally synchronized to eliminate runt pulses on the outputs during asynchronous assertion/deassertion of the clock enable pin.

ICS8305 Key Features

- Four LVCMOS / LVTTL outputs, 7 output impedance

- Selectable differential or LVCMOS / LVTTL clock inputs

- CLK, nCLK pair can accept the following differential input levels

- LVCMOS_CLK supports the following input types: LVCMOS

- Maximum output frequency: 350MHz

- Output skew: 35ps (maximum)

- Part-to-part skew: 700ps (maximum)

- Additive phase jitter, RMS: 0.04ps (typical)

- Power supply modes

- 0°C to 70°C ambient operating temperature