TC58DVG02A1F00

Overview

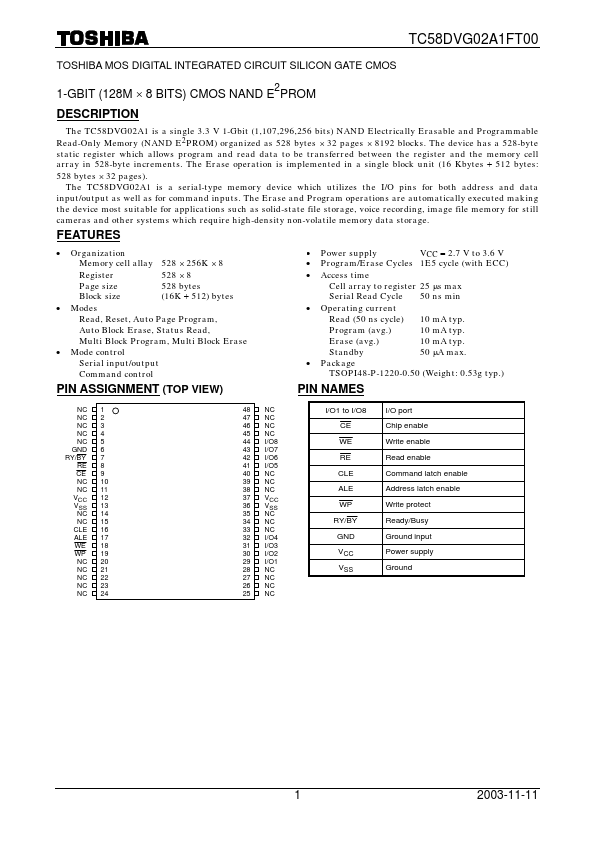

- Organization Memory cell allay 528 × 256K × 8 Register 528 × 8 Page size 528 bytes Block size (16K + 512) bytes Modes Read, Reset, Auto Page Program, Auto Block Erase, Status Read, Multi Block Program, Multi Block Erase Mode control Serial input/output Command control * * *

- Power supply VCC = 2.7 V to 3.6 V Program/Erase Cycles 1E5 cycle (with ECC) Access time Cell array to register 25 µs max Serial Read Cycle 50 ns min Operating current Read (50 ns cycle) 10 mA typ. Program (avg.) 10 mA typ. Erase (avg.) 10 mA typ. Standby 50 µA max. Package TSOPI48-P-1220-0.50 (Weight: 0.53g typ.) * *