TC58NVG0S3AFT00

DESCRIPTION

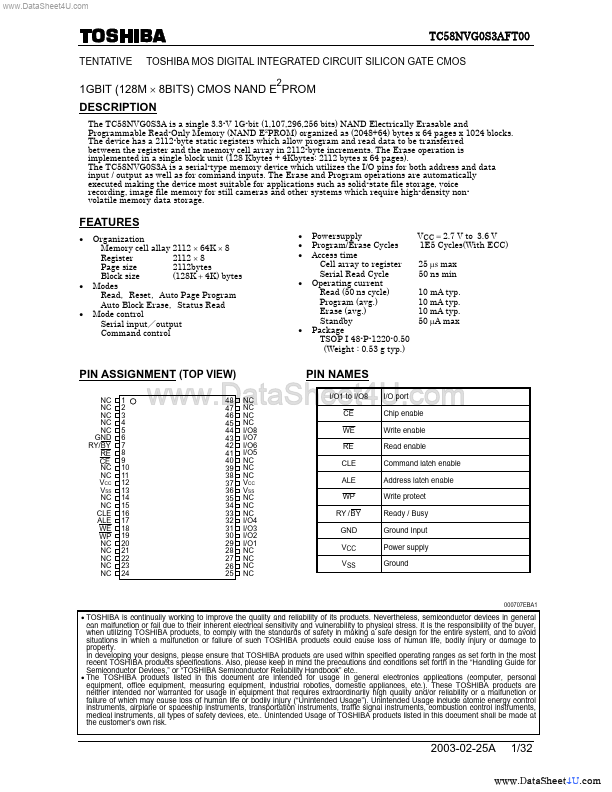

The TC58NVG0S3A is a single 3.3-V 1G-bit (1,107,296,256 bits) NAND Electrically Erasable and Programmable Read-Only Memory (NAND E2PROM) organized as (2048+64) bytes x 64 pages x 1024 blocks. The device has a 2112-byte static registers which allow program and read data to be transferred between the register and the memory cell array in 2112-byte increments. The Erase operation is implemented in a single block unit (128 Kbytes + 4Kbytes: 2112 bytes x 64 pages). The TC58NVG0S3A is a serial-type memory device which utilizes the I/O pins for both address and data input / output as well as for mand inputs. The Erase and Program operations are automatically executed making the device most suitable for applications such as solid-state file storage, voice recording, image file memory for still cameras and other systems which require high-density nonvolatile memory data storage.

FEATURES x Organization Memory cell allay 2112 u 64K u 8 Register 2112 u 8 Page size 2112bytes Block...