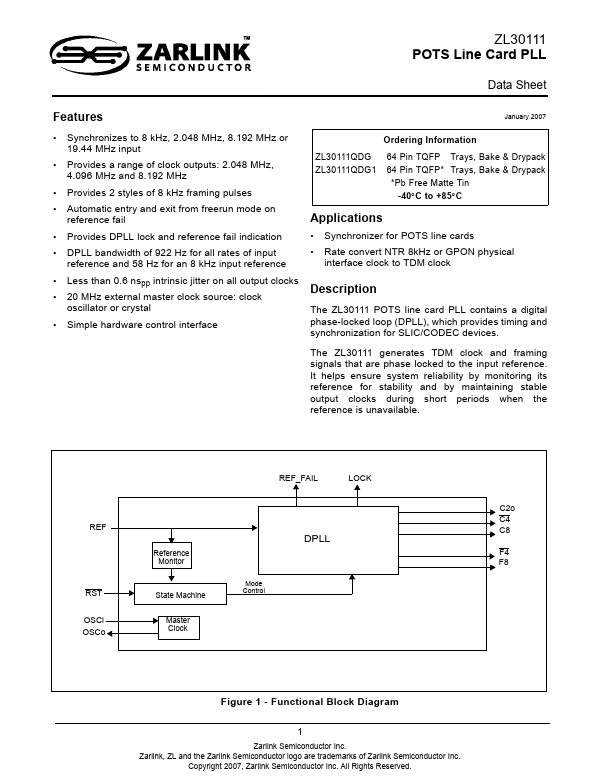

ZL30111 Description

The ZL30111 POTS line card PLL contains a digital phase-locked loop (DPLL), which provides timing and synchronization for SLIC/CODEC devices. The ZL30111 generates TDM clock and framing signals that are phase locked to the input reference. It helps ensure system reliability by monitoring its reference for stability and by maintaining stable output clocks during short periods when the reference is unavailable.