ZL30119 Overview

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 1.1.

ZL30119 Key Features

- Synchronizes with standard tele system references and synthesizes a wide variety of protected tele line interface clocks

- Internal APLL provides standard output clock frequencies up to 622.08 MHz that meet jitter requirements for interfaces u

- Programmable output synthesizers (P0, P1) generate clock frequencies from any multiple of 8 kHz up to 77.76 MHz in addit

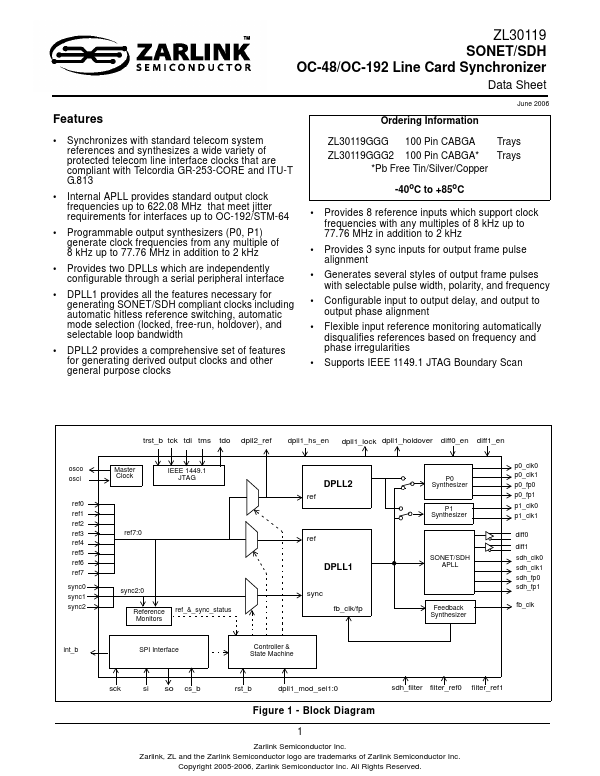

- Provides two DPLLs which are independently configurable through a serial peripheral interface

- DPLL1 provides all the features necessary for generating SONET/SDH pliant clocks including automatic hitless reference s

- DPLL2 provides a prehensive set of features for generating derived output clocks and other general purpose clocks

- Pb Free Tin/Silver/Copper

- 40oC to +85oC

- Provides 8 reference inputs which support clock frequencies with any multiples of 8 kHz up to 77.76 MHz in addition to 2

- Provides 3 sync inputs for output frame pulse alignment

ZL30119 Applications

- AMCs for AdvancedTCATM and MicroTCA Systems