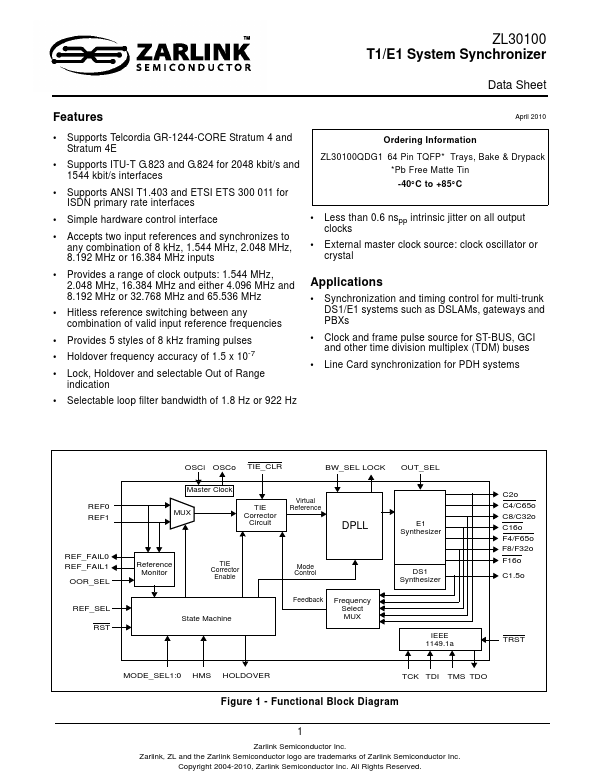

ZL30100 Overview

Key Specifications

Package: TQFP

Pins: 64

Max Operating Temp: 85 °C

Min Operating Temp: -40 °C

Key Features

- Supports Telcordia GR-1244-CORE Stratum 4 and Stratum 4E

- Supports ITU-T G.823 and G.824 for 2048 kbit/s and 1544 kbit/s interfaces

- Supports ANSI T1.403 and ETSI ETS 300 011 for ISDN primary rate interfaces