Datasheet Details

- Part number

- KM681002CI, KM681002C

- Manufacturer

- Samsung semiconductor

- File Size

- 176.29 KB

- Datasheet

- KM681002C_Samsungsemiconductor.pdf

- Description

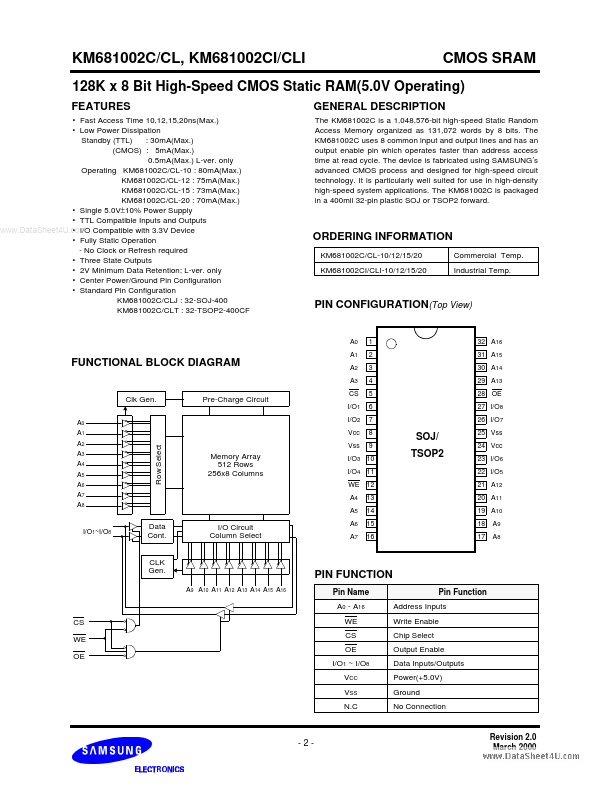

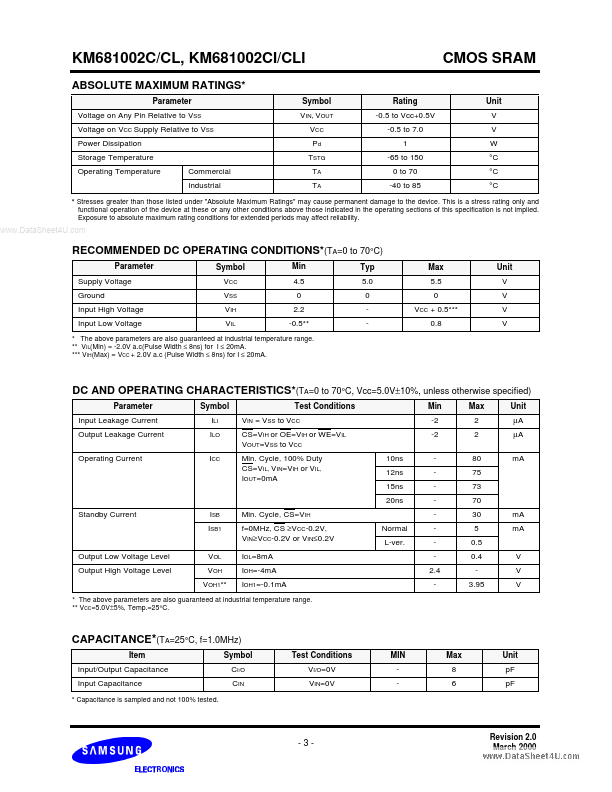

- 128Kx8 Bit High-Speed CMOS Static RAM

- Note

- This datasheet PDF includes multiple part numbers: KM681002CI, KM681002C.

Please refer to the document for exact specifications by model.