9FGL02 Overview

Key Specifications

Mount Type: Surface Mount

Pins: 24

Operating Voltage: 3.3 V

Max Voltage (typical range): 3.465 V

Description

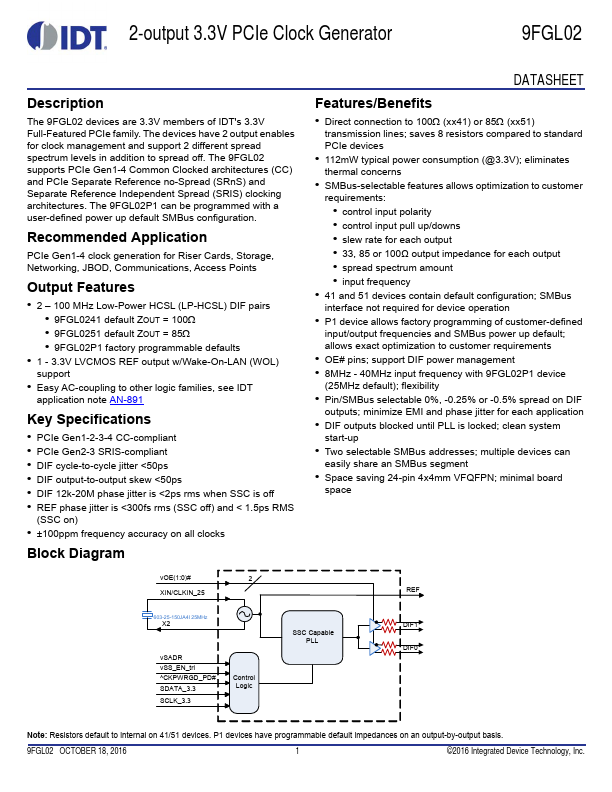

The 9FGL02 devices are 3.3V members of IDT's 3.3V Full-Featured PCIe family. The devices have 2 output enables for clock management and support 2 different spread spectrum levels in addition to spread off.

Key Features

- 2 – 100 MHz Low-Power HCSL (LP-HCSL) DIF pairs

- 9FGL0241 default ZOUT = 100

- 9FGL0251 default ZOUT = 85

- 9FGL02P1 factory programmable defaults

- 1 - 3.3V LVCMOS REF output w/Wake-On-LAN (WOL) support

- Easy AC-coupling to other logic families, see IDT