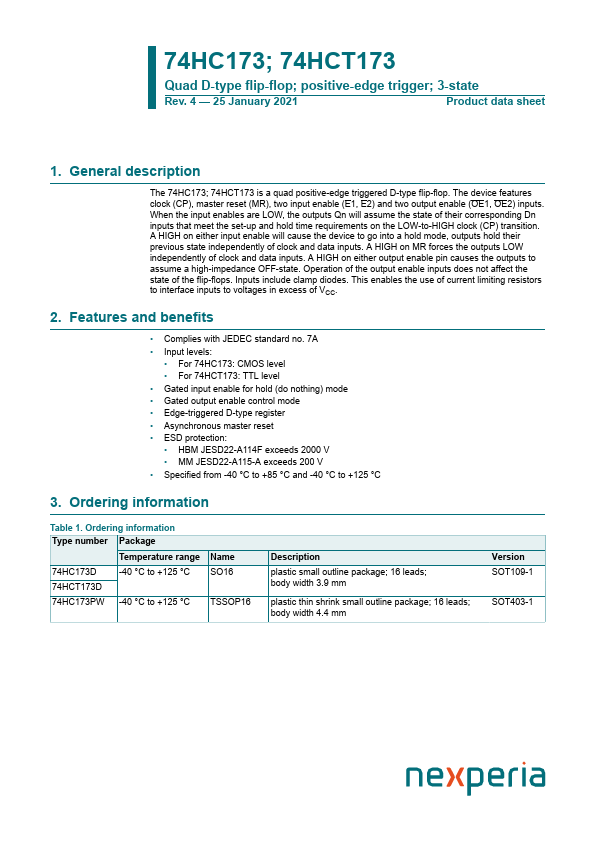

74HCT173 Overview

Key Specifications

Package: SOP

Mount Type: Surface Mount

Pins: 16

Operating Voltage: 5 V

Description

The 74HC173; 74HCT173 is a quad positive-edge triggered D-type flip-flop. The device features clock (CP), master reset (MR), two input enable (E1, E2) and two output enable (OE1, OE2) inputs.

Key Features

- Complies with JEDEC standard no. 7A

- Input levels

- For 74HC173: CMOS level

- For 74HCT173: TTL level

- Gated input enable for hold (do nothing) mode