LMK00725

Overview

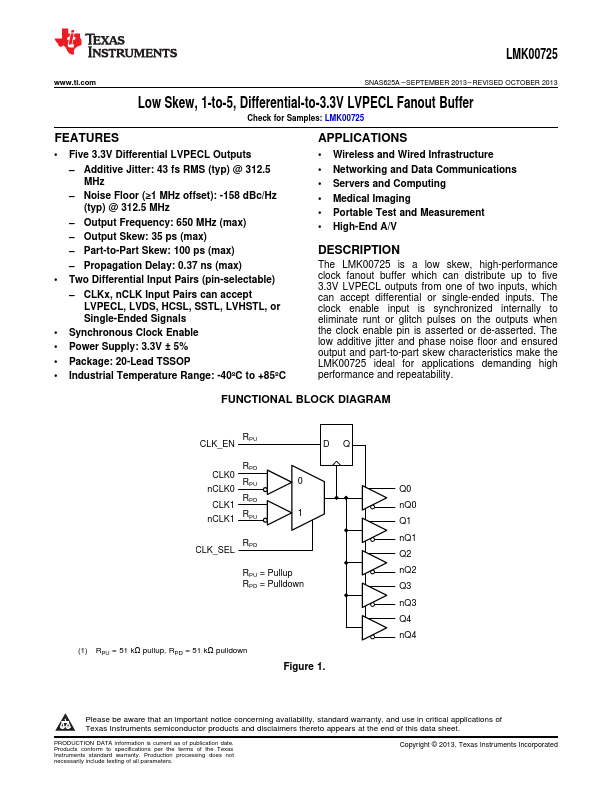

The LMK00725 is a low skew, high-performance clock fanout buffer which can distribute up to five 3.3V LVPECL outputs from one of two inputs, which can accept differential or single-ended inputs. The clock enable input is synchronized internally to eliminate runt or glitch pulses on the outputs when the clock enable pin is asserted or de-asserted.

- Five 3.3V Differential LVPECL Outputs - Additive Jitter: 43 fs RMS (typ) @ 312.5 MHz - Noise Floor (≥1 MHz offset): -158 dBc/Hz (typ) @ 312.5 MHz - Output Frequency: 650 MHz (max) - Output Skew: 35 ps (max) - Part-to-Part Skew: 100 ps (max) - Propagation Delay: 0.37 ns (max)

- Two Differential Input Pairs (pin-selectable) - CLKx, nCLK Input Pairs can accept LVPECL, LVDS, HCSL, SSTL, LVHSTL, or Single-Ended Signals

- Synchronous Clock Enable

- Power Supply: 3.3V ± 5%

- Package: 20-Lead TSSOP

- Industrial Temperature Range: -40ºC to +85ºC