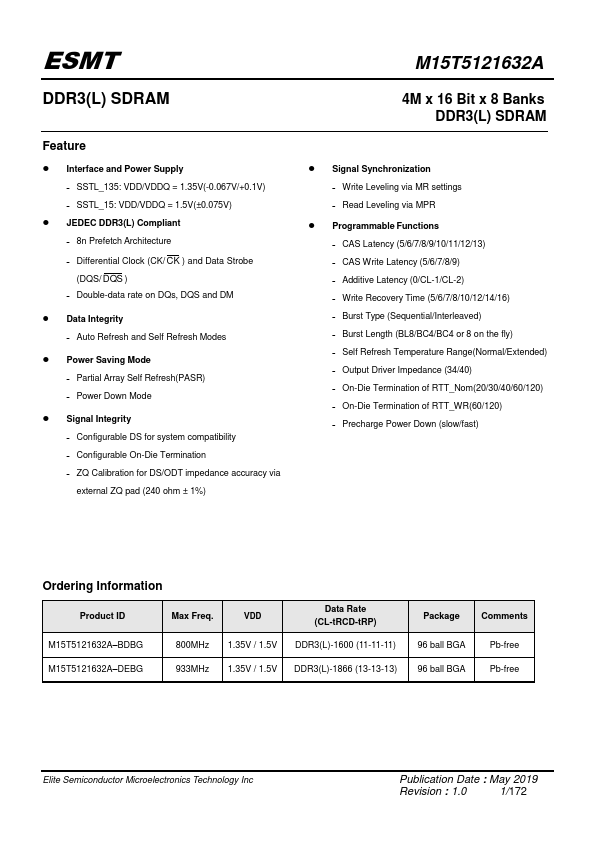

M15T5121632A Overview

Description

The 512Mb Double-Data-Rate-3 (DDR3(L)) DRAM is double data rate architecture to achieve high-speed operation. It is internally configured as an eight-bank DRAM.

Key Features

- Interface and Power Supply ˗ SSTL_135: VDD/VDDQ = 1.35V(-0.067V/+0.1V) ˗ SSTL_15: VDD/VDDQ = 1.5V(±0.075V)

- Data Integrity ˗ Auto Refresh and Self Refresh Modes

- Power Saving Mode ˗ Partial Array Self Refresh(PASR) ˗ Power Down Mode

- Signal Synchronization ˗ Write Leveling via MR settings ˗ Read Leveling via MPR