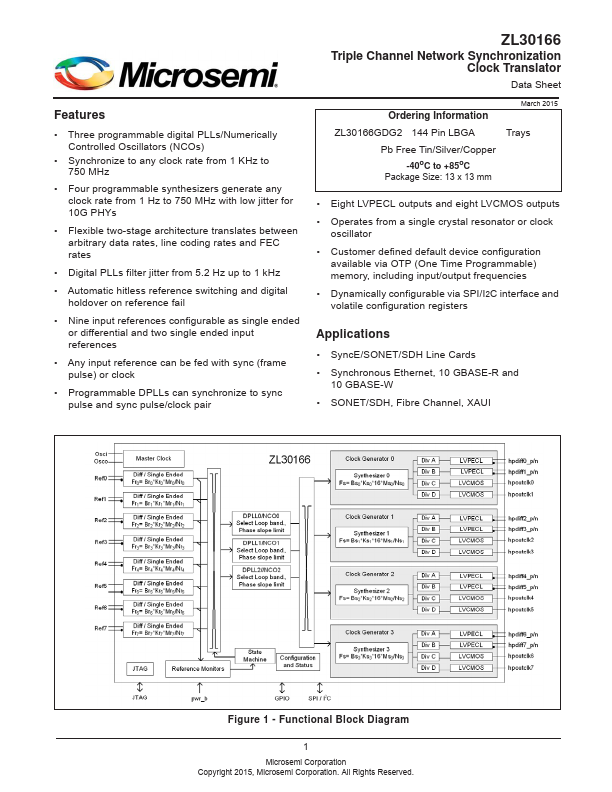

ZL30166 Overview

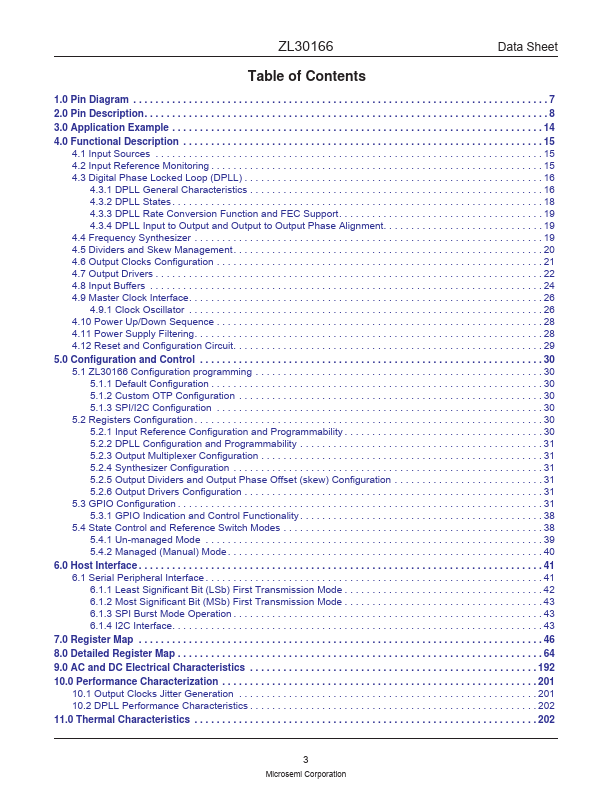

8 3.0 Application Example . 14 4.0 Functional Description . 15 4.2 Input Reference Monitoring.

ZL30166 Key Features

- Three programmable digital PLLs/Numerically Controlled Oscillators (NCOs)

- Synchronize to any clock rate from 1 KHz to 750 MHz

- Four programmable synthesizers generate any clock rate from 1 Hz to 750 MHz with low jitter for 10G PHYs

- Flexible two-stage architecture translates between arbitrary data rates, line coding rates and FEC rates

- Digital PLLs filter jitter from 5.2 Hz up to 1 kHz

- Automatic hitless reference switching and digital holdover on reference fail

- Nine input references configurable as single ended or differential and two single ended input references

- Any input reference can be fed with sync (frame pulse) or clock

- Programmable DPLLs can synchronize to sync pulse and sync pulse/clock pair

- 40oC to +85oC Package Size: 13 x 13 mm