Description

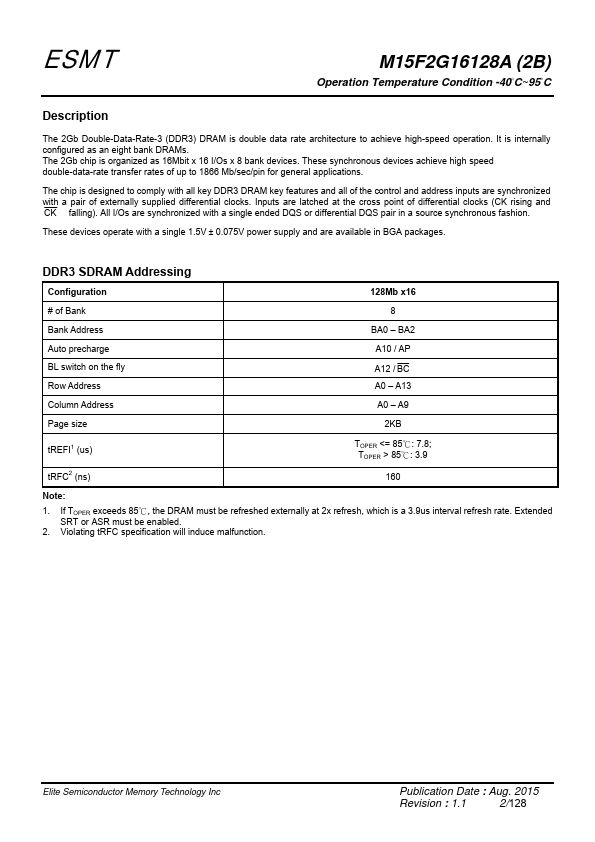

The 2Gb Double-Data-Rate-3 (DDR3) DRAM is double data rate architecture to achieve high-speed operation.

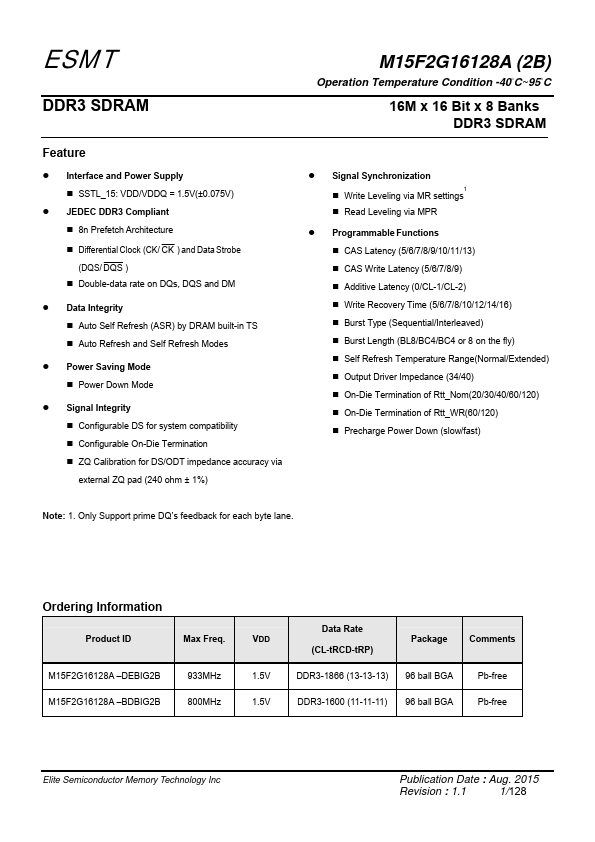

Features

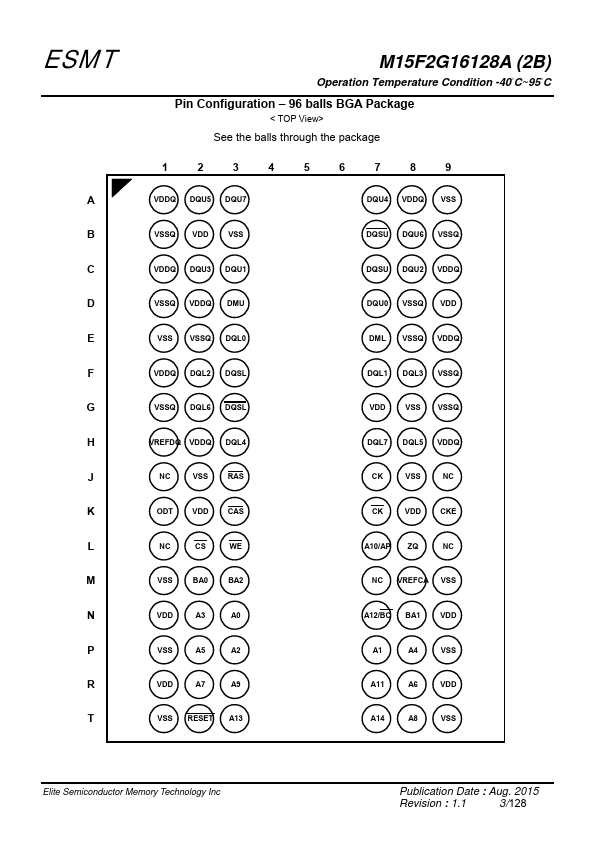

- and all of the control and address inputs are synchronized with a pair of externally supplied differential clocks. Inputs are latched at the cross point of differential clocks (CK rising and CK falling). All I/Os are synchronized with a single ended DQS or differential DQS pair in a source synchronous fashion. These devices operate with a single 1.5V ± 0.075V power supply and are available in BGA packages. DDR3 SDRAM Addressing

Configuration

128Mb x16

# of Bank

8

Bank Address

BA0.